# Programa de Doctorado de Computación Avanzada, Energía y Plasmas Universidad de Córdoba

## Tesis Doctoral

Diseño de Sistemas Embebidos Reconfigurables Empleando Elementos de Interconexión en Chip Definidos por Software

Design of Reconfigurable Embedded Systems Using Software-Defined On-Chip Interconnect Elements

Memoria presentada para optar al grado de Doctor por Salvador Ibarra Delgado

> Director: Dra. María Brox Jimenez Co-Director: Manuel Agustín Ortiz López Co-Director: Remberto Sandoval Aréchiga

> > Córdoba, 9 de mayo de 2021

## TITULO: Diseño de sistemas embebidos reconfigurables empleando elementos de interconexión en Chip definidos por Software

AUTOR: Salvador Ibarra Delgado

© Edita: UCOPress. 2021 Campus de Rabanales Ctra. Nacional IV, Km. 396 A 14071 Córdoba

https://www.uco.es/ucopress/index.php/es/ucopress@uco.es

TÍTULO DE LA TESIS: Diseño de Sistemas Embebidos Reconfigurables Empleando Elementos de Interconexión en Chip Definidos por Software

DOCTORANDO/A: Salvador Ibarra Delgado

#### INFORME RAZONADO DE LOS DIRECTORES DE LA TESIS

Esta Tesis Doctoral se centra en el desarrollo de la arquitectura de un sistema de interconexión tipo bus que opera bajo el paradigma de Redes definidas por Software en un Sistema en Chip. Los resultados incluidos en la Tesis demuestran que la infraestructura desarrollada es altamente flexible, reconfigurable, escalable, reutilizable y fácil de administrar, por lo que se incrementan las prestaciones otorgadas por los modelos tradicionales de interconexión tipo bus.

Durante el desarrollo de la Tesis Doctoral, el doctorando ha demostrado una gran capacidad de organización y trabajo autónomo adaptándose y buscando soluciones para resolver los diferentes problemas que han ido apareciendo en el transcurso de la misma. Por tanto, se pone de manifiesto que el doctorando ha adquirido las competencias necesarias para el desarrollo de una prometedora carrera científica.

Por todo lo reflejado en este informe, los directores consideramos que esta Tesis Doctoral posee un gran calidad y prueba de ello es que los resultados derivados de ella han sido publicados en una revista de segundo cuartil y otra de cuarto cuartil (JCR):

-Ibarra-Delgado S., Sandoval-Arechiga R., Gómez-Rodríguez J.R., Ortíz-López M. and Brox M. A Bandwidth Control Arbitration for SoC Interconnections Performing Applications with Task Dpendencies. Micromachines 2020, 11(12), 1063.

-Ibarra-Delgado S., Sandoval-Arechiga R., Brox M. and Ortíz-López M. Throughput Unfairness in Fair Arbitration Interconnection-Buses for Aerospace Embedded Systems. IEEE Latin America Transactions 2020, 18(9), 1606.

Por todo ello, se autoriza la presentación de la Tesis Doctoral.

Córdoba, España, 22 de abril de 2021

Firma de los directores

BROX JIMENEZ JIMENEZ JIMENEZ MARIA - 30649385 MARIA - MARIA -

MARIA -30964938S rimado digitalmente por BrUX

JinieNez Mariki - 300649383

Nombre de reconocimiento (DN):

c=5.

sertalNumberiiDCE5-309649385.

givenName-MARIA, sn=BROX

JIMENEZ, cn=BROX JIMENEZ MARIA300649385

Fecha: 2021 04.25 08:08:58 +02:00

Fdo.: Dra. María Brox Jiménez

Firmado por ORTIZ LOPEZ MANUEL AGUSTIN - 24199639M el día 26/04/2021 con un certificado emitido por AC

Fdo.: Dr. Manuel Agustín Ortiz López

Fdo.: Dr. Remberto Sandoval Aréchiga

#### Abstract

The set of applications that today run in the processing elements inside a Systemon-Chip (SoC) require that the SoC interconnection system allows them to meet the Quality of Service (QoS) requirements that were established. Current interconnection systems must be flexible, reconfigurable, scalable, reusable and easy to manage. This document presents a solution for a bus type interconnection system, based on the Software Defined Network (SDN) paradigm. The work shows the general architecture of the interconnection system and demonstrates that this architecture meets the characteristics mentioned above. The work puts special emphasis on the infrastructure layer of the system — hardware —. However, it also establishes the elements to be included in the network operating system layer and its interrelation with the adjacent layers. This work also shows a new arbitration policy based on budgets that allows the differentiated use of the bus. The policy presents the best behavior when the system works in scenarios with applications executing dependent tasks, which are very common nowadays. The system was modeled in SystemC with clock cycle accuracy. The contributions made in this work can be extrapolated to other SoC interconnection systems because the challenges they share are similar.

#### Resumen

El conjunto de aplicaciones que hoy en día se ejecutan en los elementos de procesamiento en el interior de un Sistema en Chip (System-on-Chip (SoC), en inglés) requieren que el sistema de interconexión que los conecta, les permita cumplir con los requerimientos de Calidad en el Servicio (Quality of Service (QoS), en inglés) que les fueron establecidos. Los actuales sistemas de interconexión deben ser flexibles, reconfigurables, escalables, reutilizables y fáciles de administrar. En este documento se presenta una solución para un sistema de interconexión tipo bus basado en el paradigma de Redes Definidas por Software (Software Defined Network (SDN), en inglés). El trabajo muestra la arquitectura general del sistema de interconexión y en él se demuestra que la arquitectura cumple con las características anteriormente mencionadas. El trabajo pone especial énfasis en la capa de infraestructura del sistema – hardware–. Además, se incluyen los elementos de la capa de sistema operativo de red y se establecen sus interrelaciones con las capas advacentes. En este trabajo también se muestra una nueva política de arbitraje basada en presupuestos la cual permite el uso diferenciado del bus. La política muestra un mejor comportamiento cuando el sistema funciona en escenarios ejecutando aplicaciones con tareas dependientes, los cuales son muy comunes en la actualidad. El sistema fue modelado en SystemC con precisión de ciclo de reloj. Las contribuciones realizadas en este trabajo pueden ser extrapoladas a otros sistemas de interconexión en SoC debido a que los retos que comparten son similares.

## Índice general

| In           | dice         | de figuras                                                                  | V                      |  |  |  |  |

|--------------|--------------|-----------------------------------------------------------------------------|------------------------|--|--|--|--|

| Ín           | dice         | de tablas                                                                   | IX                     |  |  |  |  |

| Sig          | $_{ m glas}$ |                                                                             | x                      |  |  |  |  |

| $\mathbf{G}$ | osari        | io                                                                          | $\mathbf{x}\mathbf{v}$ |  |  |  |  |

| 1.           | Intr         | oducción                                                                    | 1                      |  |  |  |  |

|              | 1.1.         | Antecedentes                                                                | 1                      |  |  |  |  |

|              | 1.2.         | Justificación                                                               | 2                      |  |  |  |  |

|              | 1.3.         | Alcances                                                                    | 5                      |  |  |  |  |

|              | 1.4.         | Planteamiento del problema                                                  | 6                      |  |  |  |  |

|              | 1.5.         | Objetivos                                                                   | 8                      |  |  |  |  |

|              | 1.6.         | Metodología                                                                 | 8                      |  |  |  |  |

|              | 1.7.         | Contribuciones                                                              | 10                     |  |  |  |  |

|              | 1.8.         | Publicaciones Científicas Relacionadas                                      | 10                     |  |  |  |  |

|              | 1.9.         | Estructura general de la tesis                                              | 11                     |  |  |  |  |

| 2.           | Mar          | Marco Teórico                                                               |                        |  |  |  |  |

|              | 2.1.         | Sistemas-en-Chip                                                            | 14                     |  |  |  |  |

|              |              | 2.1.1. Reusabilidad                                                         | 14                     |  |  |  |  |

|              |              | 2.1.2. Integración                                                          | 16                     |  |  |  |  |

|              |              | 2.1.3. Calidad del Servicio                                                 | 17                     |  |  |  |  |

|              |              | 2.1.4. Mapeo de Aplicaciones                                                | 18                     |  |  |  |  |

|              | 2.2.         | Sistemas de Interconexión en Sistemas en Chip                               | 18                     |  |  |  |  |

|              |              | 2.2.1. Bus                                                                  | 20                     |  |  |  |  |

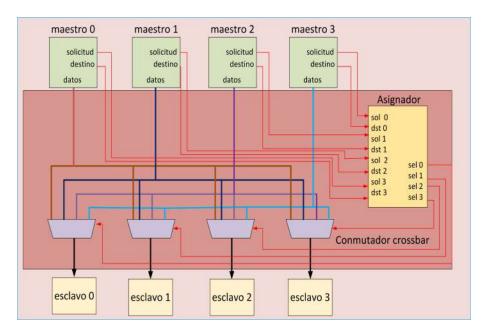

|              |              | 2.2.2. Crossbar                                                             | 21                     |  |  |  |  |

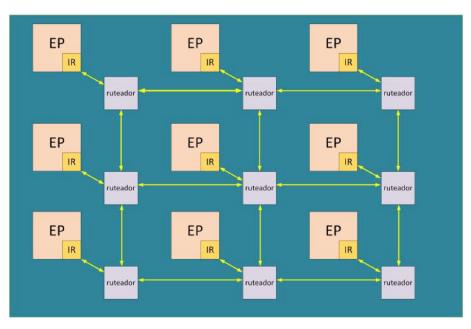

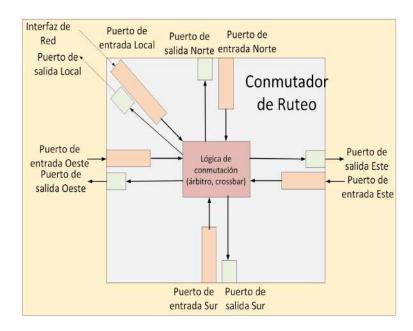

|              |              | 2.2.3. Network-on-Chip                                                      | 22                     |  |  |  |  |

|              | 2.3.         | Ventajas/Desventajas de los Sistemas de Interconexión para Sistemas en Chip | 24                     |  |  |  |  |

|    |      | 2.3.1. Bus                                                           | 25  |  |  |  |  |

|----|------|----------------------------------------------------------------------|-----|--|--|--|--|

|    |      | 2.3.2. Crossbar                                                      | 26  |  |  |  |  |

|    |      | 2.3.3. Network-on-Chip                                               |     |  |  |  |  |

|    | 2.4. | Arbitraje                                                            | 27  |  |  |  |  |

|    |      | 2.4.1. Necesidad del Arbitraje                                       | 27  |  |  |  |  |

|    |      | 2.4.2. Políticas de Arbitraje                                        | 28  |  |  |  |  |

|    | 2.5. | Principios de Redes Definidas por Software                           | 44  |  |  |  |  |

|    |      | 2.5.1. Introducción a Redes Definidas por Software                   | 45  |  |  |  |  |

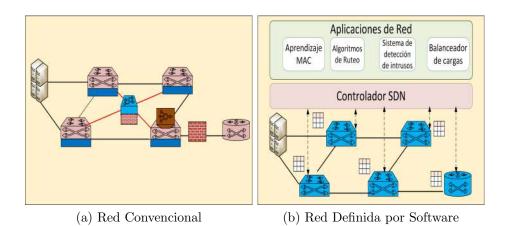

|    |      | 2.5.2. Redes Convencionales Vs Redes Definidas por Software          | 47  |  |  |  |  |

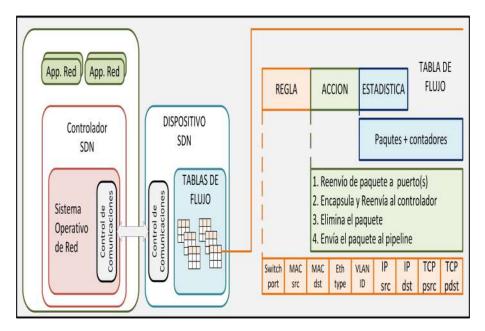

|    |      | 2.5.3. Terminología de Redes Definidas por Software                  | 47  |  |  |  |  |

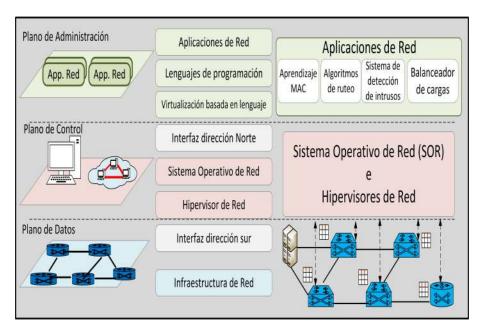

|    |      | 2.5.4. Arquitectura de Redes Definidas por Software                  | 49  |  |  |  |  |

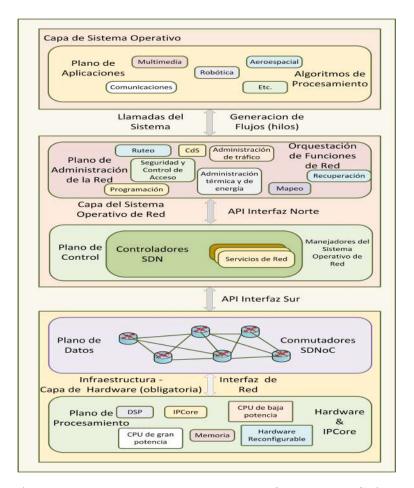

|    | 2.6. | Sistemas en Chip con enfoque de Redes Definidas por Software         | 53  |  |  |  |  |

|    |      | 2.6.1. Antecedentes                                                  | 53  |  |  |  |  |

|    |      | 2.6.2. Arquitecturas de Sistemas en Chip con enfoque de Redes De-    |     |  |  |  |  |

|    |      | finidas por Software                                                 | 57  |  |  |  |  |

|    | 2.7. | Diferencias entre Sistemas de Interconexión Tradicionales y Sistemas |     |  |  |  |  |

|    |      | de Interconexión Definidos por Software                              | 63  |  |  |  |  |

|    | 2.8. | Infraestructura para implementar Sistemas de Interconexión definidos |     |  |  |  |  |

|    |      | por software en SoC                                                  | 64  |  |  |  |  |

| 3. | Mo   | Modelo del Sistema 66                                                |     |  |  |  |  |

|    | 3.1. | Topología                                                            | 66  |  |  |  |  |

|    | 3.2. | Suite MCSL-NoC de modelado de tráfico para Redes en Chip             | 67  |  |  |  |  |

|    | 3.3. | Otras aplicaciones utilizadas para generar tráfico en la red         | 68  |  |  |  |  |

|    | 3.4. | Modelo del Sistema                                                   | 71  |  |  |  |  |

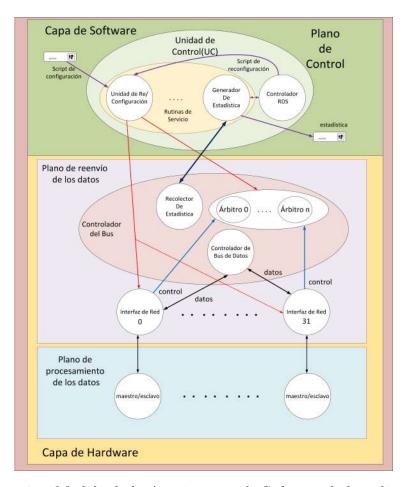

|    |      | 3.4.1. Capa de Software                                              | 72  |  |  |  |  |

|    |      | 3.4.2. Capa de Hardware                                              | 75  |  |  |  |  |

|    | 3.5. | Herramientas Adicionales                                             | 77  |  |  |  |  |

|    | 3.6. | Consideraciones                                                      | 77  |  |  |  |  |

| 4. | Arq  | rquitectura Software Defined Bus-on-Chip 79                          |     |  |  |  |  |

|    | 4.1. | Arquitectura General                                                 | 79  |  |  |  |  |

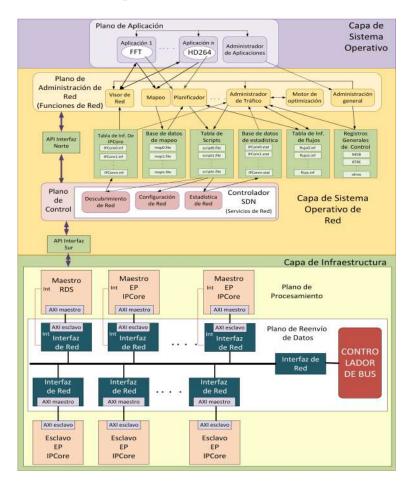

|    | 4.2. | Capa de Sistema Operativo                                            | 80  |  |  |  |  |

|    |      | 4.2.1. Plano de Aplicación                                           | 81  |  |  |  |  |

|    | 4.3. | Capa de Sistema Operativo de Red                                     | 82  |  |  |  |  |

|    | 4.4. | Capa de Infraestructura                                              | 90  |  |  |  |  |

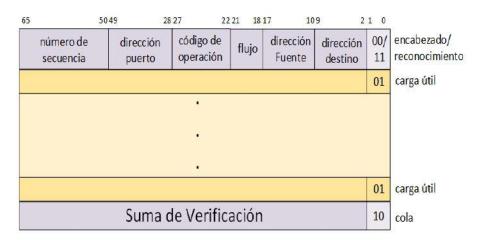

|    |      | 4.4.1. Estructura de los paquetes de datos                           | 90  |  |  |  |  |

|    |      | 4.4.2. Plano de Procesamiento de Datos                               | 91  |  |  |  |  |

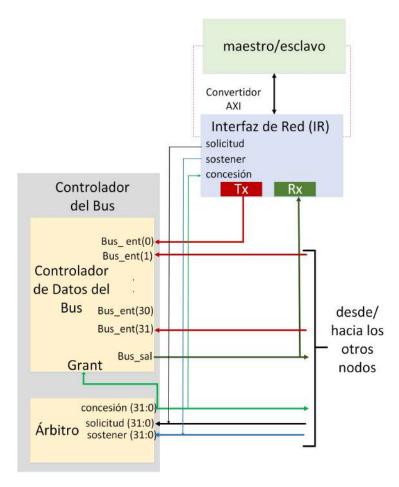

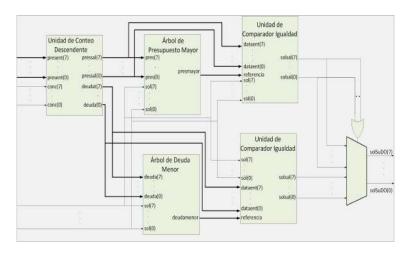

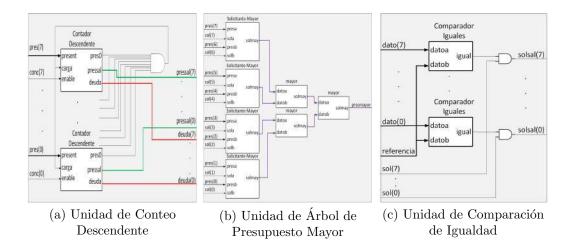

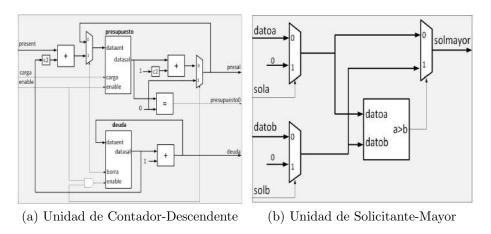

|    |      | 4.4.3. Plano de Reenvío de Datos                                     | 98  |  |  |  |  |

|    | 4.5. | Operación del Bus-en-Chip Definido por Software                      | 118 |  |  |  |  |

#### ÍNDICE GENERAL

|           | 4.6. |         | sis de la Implementación Hardware del Bus-en-Chip Definido oftware |       |

|-----------|------|---------|--------------------------------------------------------------------|-------|

| <b>5.</b> | Res  | ultado  | s                                                                  | 124   |

|           | 5.1. | Consid  | deraciones Generales                                               | . 124 |

|           | 5.2. | Clasifi | cación de Aplicaciones                                             | . 126 |

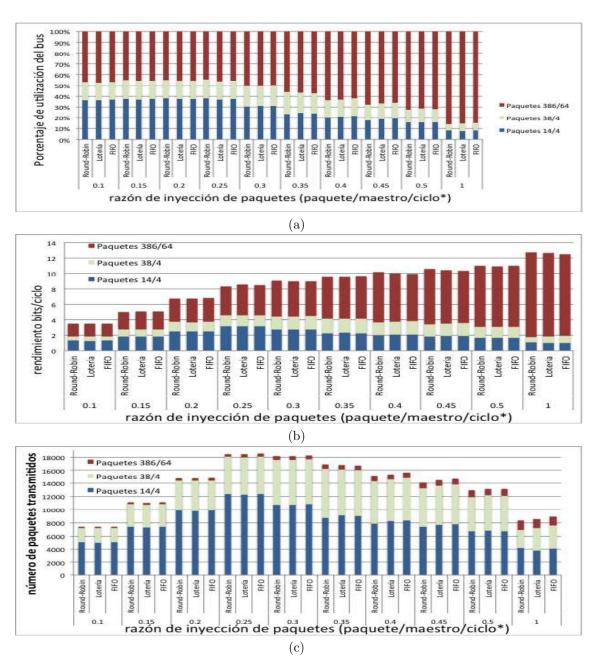

|           | 5.3. | Selecc  | ión de la política de arbitraje                                    | . 127 |

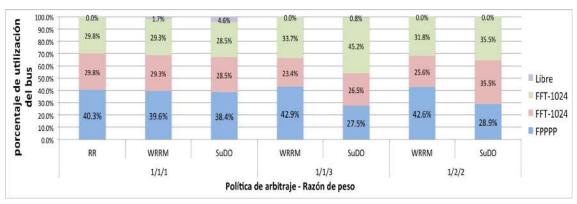

|           |      | 5.3.1.  | Políticas con acceso justo/rendimiento injusto                     | . 127 |

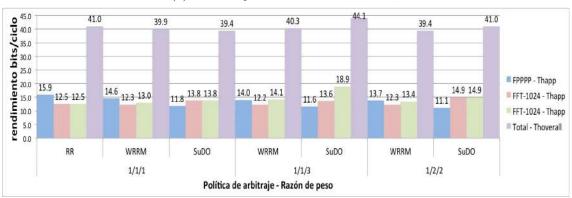

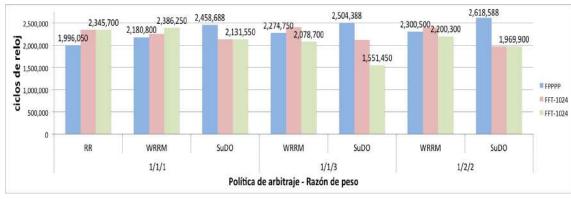

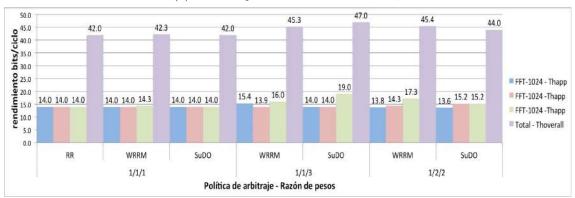

|           |      | 5.3.2.  | Políticas con Regulación del uso del bus con aplicaciones con      |       |

|           |      |         | tareas dependientes                                                | . 131 |

|           | 5.4. | Opera   | ción SDBoC                                                         | . 139 |

|           |      |         | Ventajas del uso de flujos en un sistema de interconexión tipo     |       |

|           |      |         | bus                                                                | . 139 |

|           |      | 5.4.2.  | Ejecución de procesos con direcciones multicast                    | . 143 |

|           |      |         | Operación con múltiples flujos                                     |       |

|           |      | 5.4.4.  | Recolección de estadística                                         | . 146 |

|           |      | 5.4.5.  | Reconfiguración de flujos                                          |       |

| 6.        | Con  | clusio  | nes                                                                | 151   |

| Α.        | Dia  | grama   | s de Máquinas de Estados Finitos                                   | 155   |

## Índice de figuras

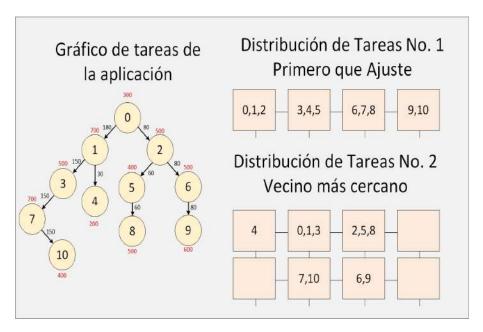

| 2.1.  | Ejemplo de mapeo de una aplicación utilizando dos técnicas diferentes                                                                         |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | García Morales et al. (2019)                                                                                                                  | 19 |

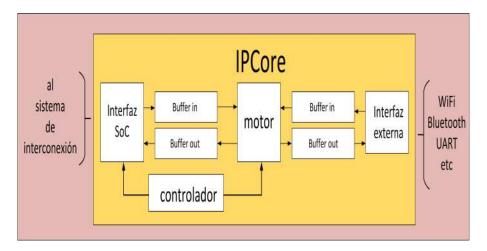

| 2.2.  | Arquitectura de un IPCore                                                                                                                     | 20 |

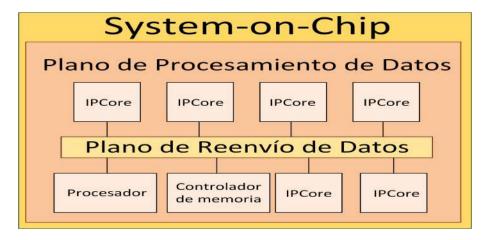

| 2.3.  | Arquitectura básica de un SoC                                                                                                                 | 20 |

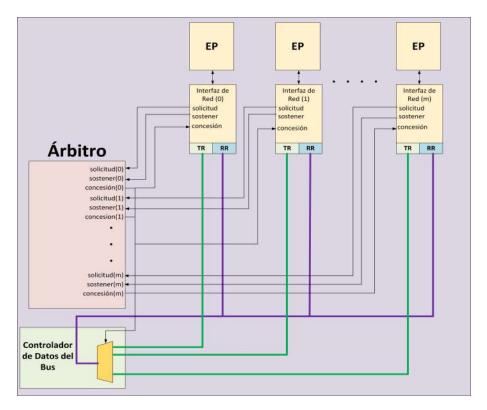

| 2.4.  | Infraestructura básica de un Sistema de Interconexión basado en Bus                                                                           | 22 |

| 2.5.  | Infraestructura básica de un Sistema de Interconexión tipo Crossbar .                                                                         | 23 |

| 2.6.  | Infraestructura básica de un Sistema de Interconexión basado en una                                                                           |    |

|       | NoC                                                                                                                                           | 24 |

| 2.7.  | Arquitectura básica de un $ruteador$ para una NoC                                                                                             | 25 |

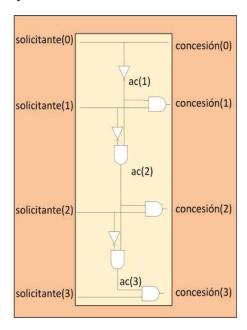

| 2.8.  | Arquitectura de un Árbitro de Prioridad Fija Dally and Towles (2001)                                                                          | 29 |

| 2.9.  | Arquitectura de un árbitro con prioridad Variable Dally and Towles                                                                            |    |

|       | $(2001) \ldots \ldots$ | 30 |

| 2.10. | Arquitectura de un Árbitro Round-Robin Dally and Towles (2001)                                                                                | 32 |

| 2.11. | Arquitectura de un Árbitro de Matriz Dally and Towles (2001)                                                                                  | 33 |

|       | Arquitectura de un árbitro de Cola de Espera Dally and Towles (2001)                                                                          | 34 |

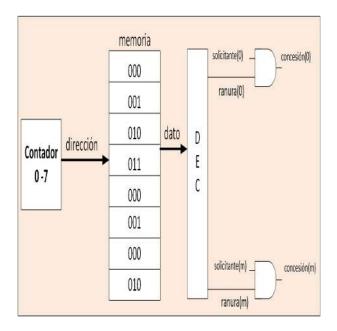

| 2.13. | Arquitectura de un árbitro TDMA                                                                                                               | 35 |

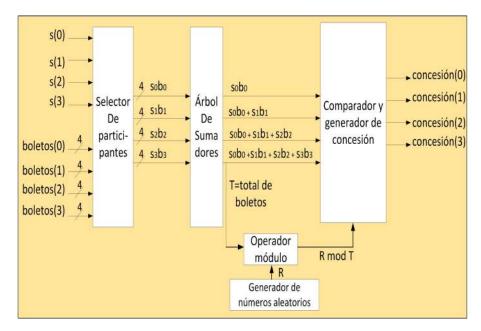

|       | Arquitectura de un Árbitro de Lotería Dinámica Lahiri et al. (2006) .                                                                         | 36 |

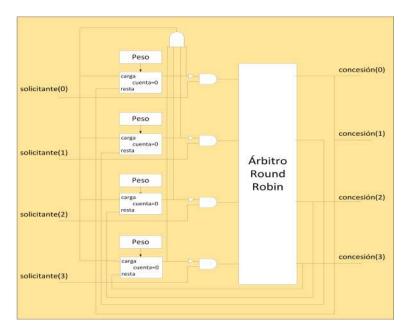

|       | Arquitectura de un árbitro WRR Dally and Towles (2001)                                                                                        | 37 |

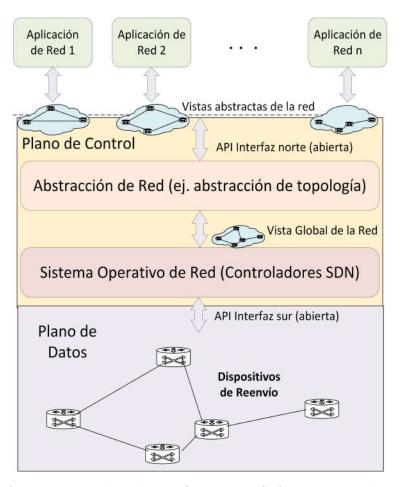

| 2.16. | Arquitectura de Redes Definidas por Software y sus abstracciones                                                                              |    |

|       | fundamentales Kreutz et al. (2015)                                                                                                            | 46 |

| 2.17. | Arquitectura Red Convencional Vs Red Definida por Software Kreutz                                                                             |    |

|       | et al. (2015)                                                                                                                                 | 48 |

| 2.18. | Planos y Niveles de la Arquitectura de Redes Definidas por Software                                                                           |    |

|       | Kreutz et al. (2015)                                                                                                                          | 49 |

| 2.19. | Proceso de comunicación entre un Controlador SDN y un Dispositivo                                                                             |    |

| 2.20  | SDN con OpenFlow Kreutz et al. (2015)                                                                                                         | 51 |

| 2.20. | Arquitectura de Interconexiones Definidas por Software Sandoval-                                                                              |    |

|       | Arechiga et al. (2017)                                                                                                                        | 58 |

| 3.1.  | Modelo de la Arquitectura de Software de la aplicación                                                                                        | 73 |

|       |                                                                                                                                               |    |

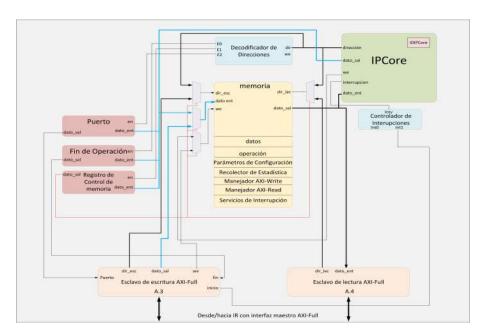

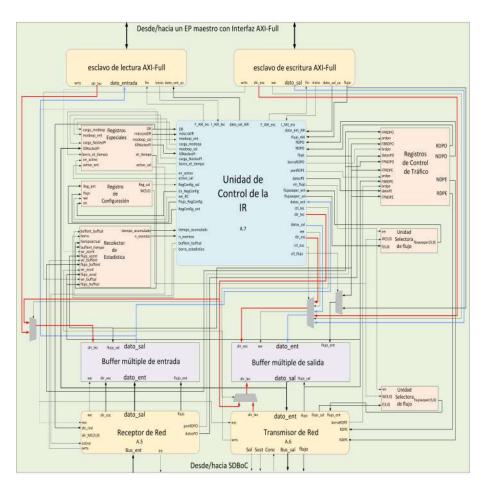

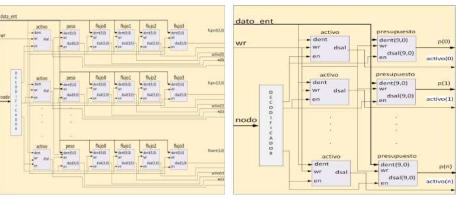

| 3.2.         | Modelo de la Arquitectura de Hardware de la aplicación                      |

|--------------|-----------------------------------------------------------------------------|

| 4.1.         | Arquitectura Bus-on-Chip bajo el paradigma Definido por Software . 80       |

| 4.2.         | Estructura general de un paquete de datos                                   |

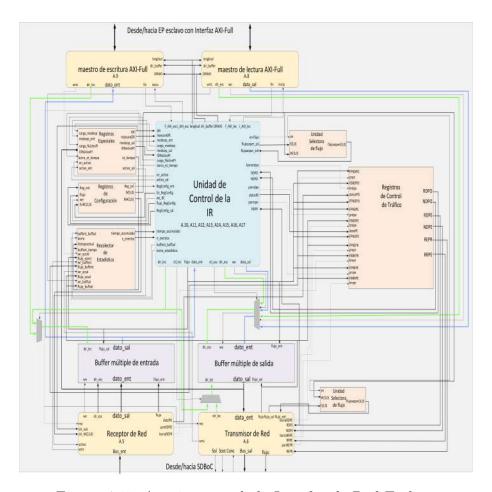

| 4.3.         | Arquitectura de un maestro con Interfaz AXI 94                              |

| 4.4.<br>4.5. | Arquitectura de un esclavo con Interfaz AXI                                 |

|              | tipo maestro                                                                |

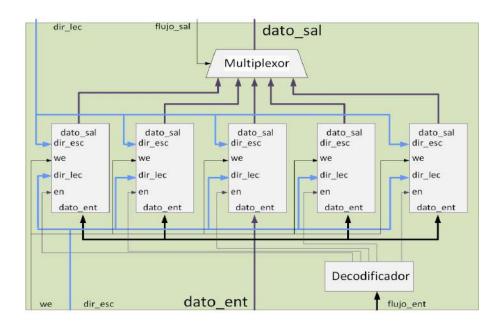

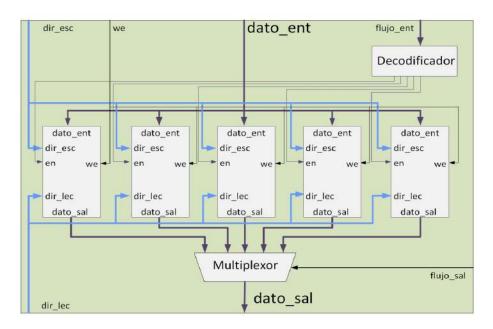

| 4.6.         | Diagrama del Buffer Múltiple de Entrada                                     |

|              | Diagrama del Buffer Múltiple de Salida                                      |

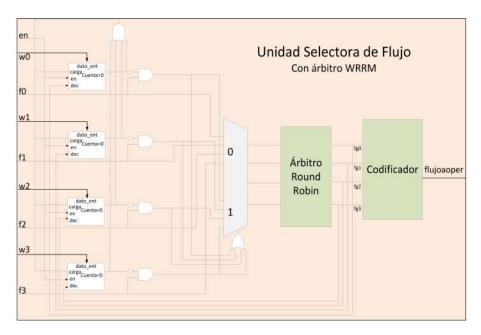

| 4.8.         | Arquitectura de la Unidad Selectora de Flujo                                |

| 4.9.         |                                                                             |

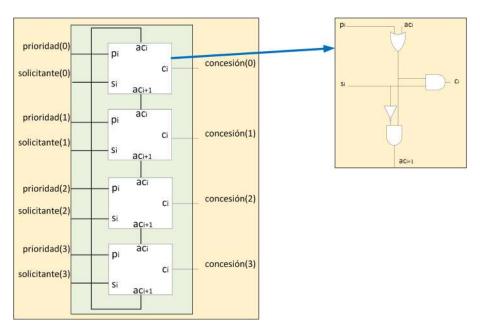

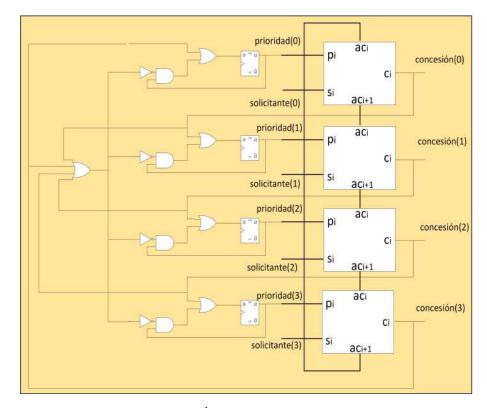

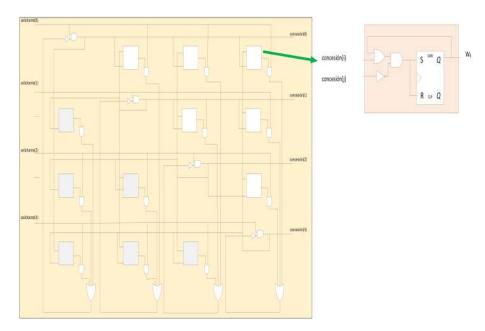

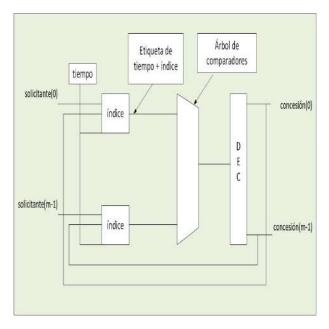

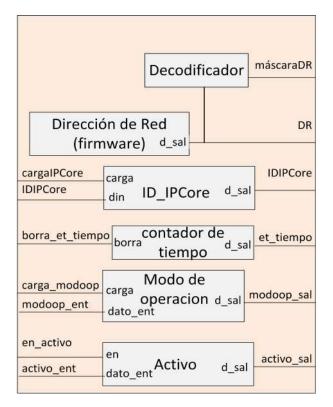

|              | Arquitectura de la Unidad de Registros de Configuración 105                 |

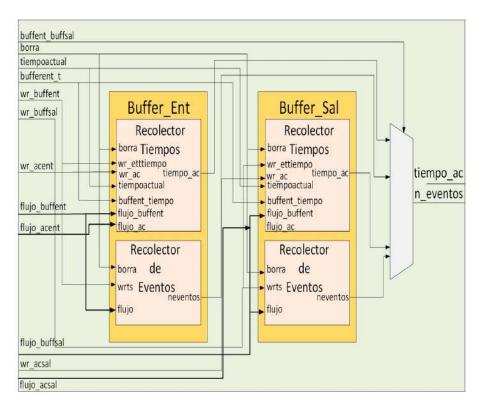

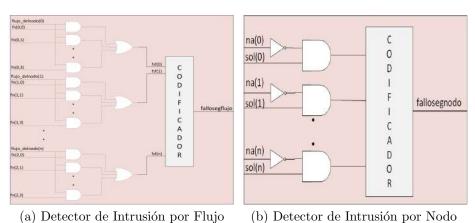

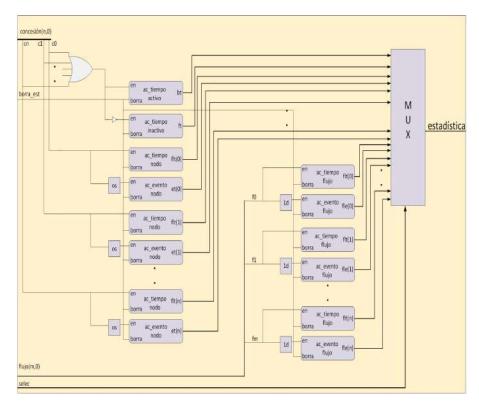

|              | Diagrama general del Recolector de Estadística                              |

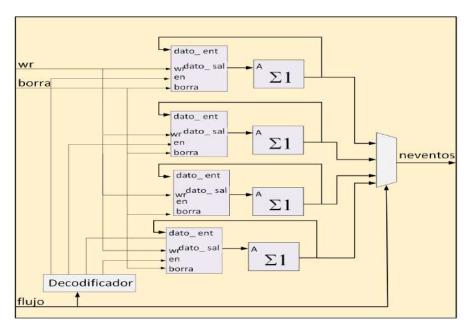

|              | Diagrama del Recolector de Eventos                                          |

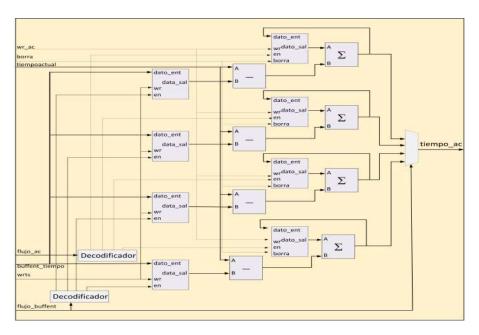

|              | Diagrama del Recolector de Tiempos de Almacenamiento 108                    |

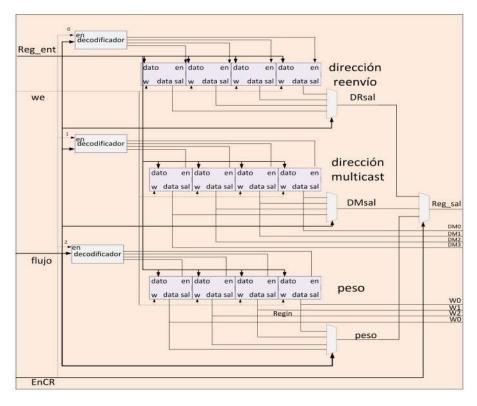

|              | Diagrama de la Unidad de Registros Controladores de Tráfico 109             |

|              | Arquitectura de la Interfaz de Red Esclava                                  |

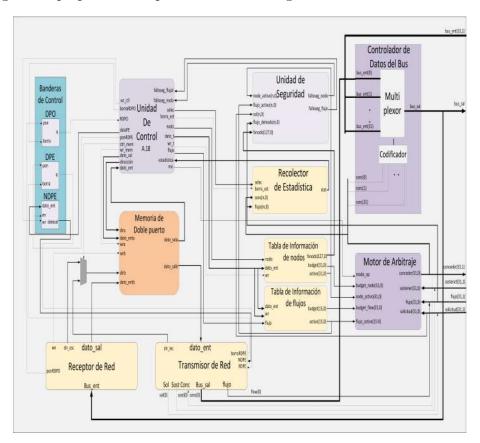

|              | Arquitectura del Controlador del Bus                                        |

|              | Elementos de la Unidad de Seguridad                                         |

|              | Diagrama del Recolector de Estadística                                      |

|              | Tablas de información                                                       |

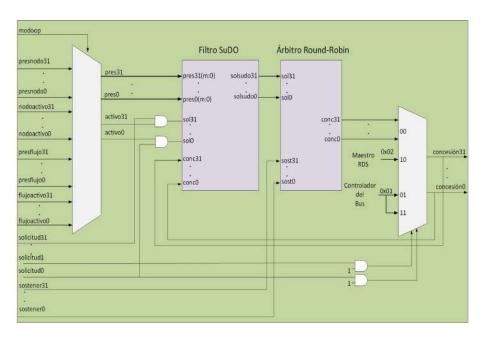

|              | Arquitectura del Motor de Arbitraje con política basada en presupuestos 117 |

|              | Arquitectura del Filtro SuDO                                                |

|              | Principales elementos del filtro SuDO                                       |

| 4.23.        | Unidades de los elementos Contador-Descendente y Solicitante-Mayor 119      |

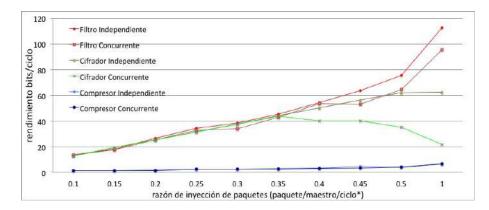

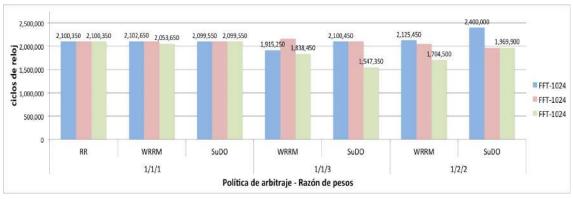

| 5.1.         | Comportamiento de las políticas de arbitraje con aplicaciones hete-         |

|              | rogéneas generando tráfico sintético                                        |

| 5.2.         | Comportamiento de la aplicación espacial cuando se varía la tasa de         |

|              | inyección de paquetes utilizando la política de arbitraje Lotería 130       |

| 5.3.         | Comportamiento de la política de arbitraje Lotería con tráfico hete-        |

|              | rogéneo y pesos de soporte diferentes                                       |

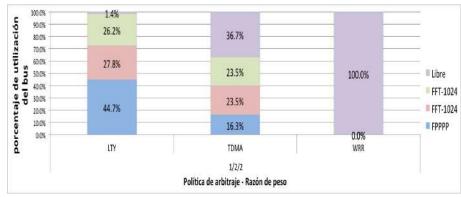

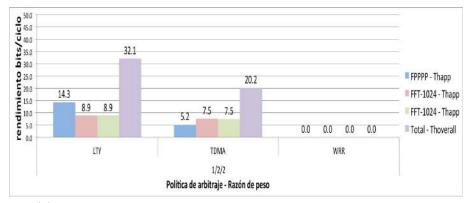

| 5.4.         | Algunos problemas detectados con políticas tradicionales corriendo en       |

|              | escenarios heterogéneos con aplicaciones dependientes. LTY tiene un         |

|              | control deficiente del ancho de banda. TDMA degrada la utilización          |

|              | del bus. WRR produce problemas de starvation y deadlock 136                 |

| 5.5.         | SuDO supera a las demás políticas de arbitraje en términos de control       |

|              | de ancho de banda en sistemas con maestros ejecutando diferentes            |

|              | aplicaciones con tareas dependientes                                        |

| 5.6.  | SuDO supera a las demás políticas de arbitraje en términos de con-             |     |

|-------|--------------------------------------------------------------------------------|-----|

|       | trol de ancho de banda cuando en el sistema se ejecutan aplicaciones           |     |

|       | iguales con tareas dependientes                                                | 140 |

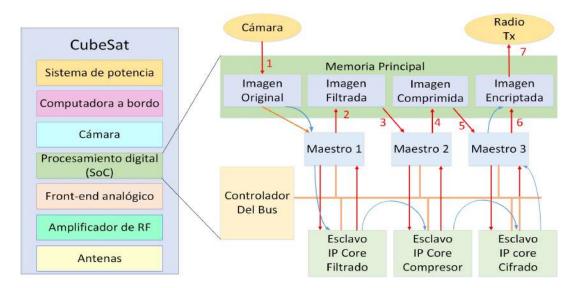

| 5.7.  | Arquitectura del sistema embebido CubeSat. Se muestra el flujo de              |     |

|       | datos de la aplicación empleada                                                | 141 |

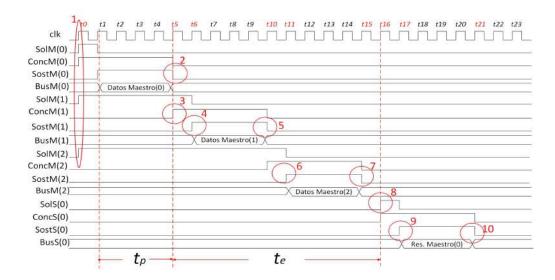

| 5.8.  | Diagrama temporal de las señales del bus con la técnica Split—                 |     |

|       | Transaction. El tiempo disponible $t_e$ entre transacciones del maestro        |     |

|       | 0 es aprovechado por transacciones de otros maestros, mejorando la             |     |

|       | utilización del bus.                                                           | 143 |

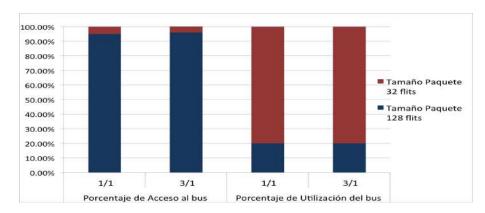

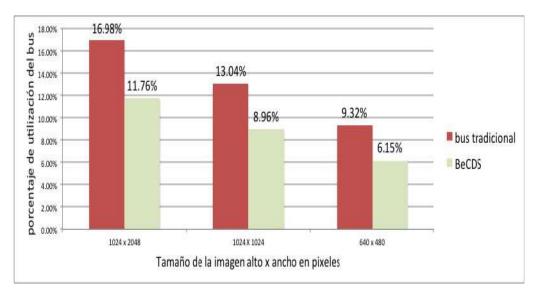

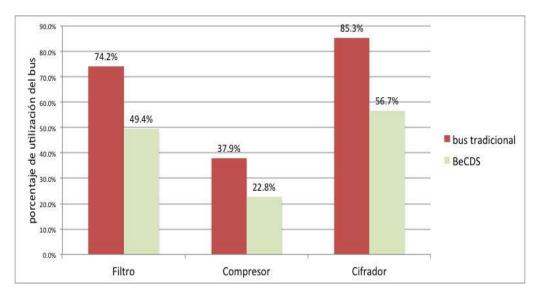

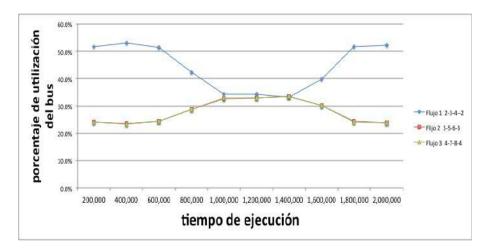

| 5.9.  | El uso de flujos en SDBoC le permite un menor porcentaje del uso               |     |

|       | del bus                                                                        | 144 |

| 5.10. | El uso de direcciones multicast para la ejecución en paralelo de múlti-        |     |

|       | ples instancias del mismo proceso en SDBoC, permite un menor por-              |     |

|       | centaje del uso del bus                                                        | 145 |

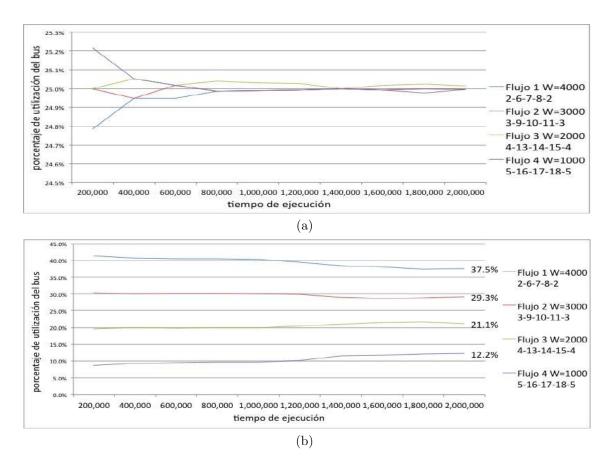

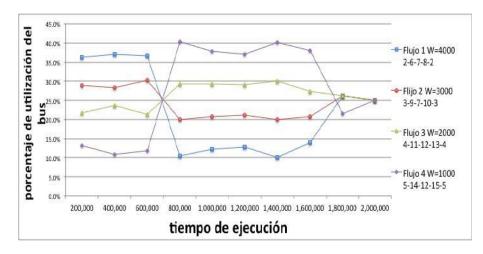

| 5.11. | SDBoC operando cuatro flujos con nodos independientes. El porcen-              |     |

|       | taje de utilización del bus corresponde con el peso establecido                | 146 |

| 5.12. | SDBoC operando cuatro flujos con nodos compartidos. El porcentaje              |     |

|       | de utilización del bus corresponde con el peso establecido                     | 147 |

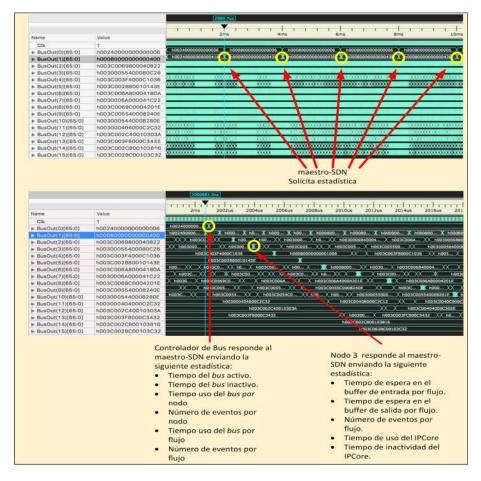

| 5.13. | Extracto de traza de datos generada al correr una simulación donde             |     |

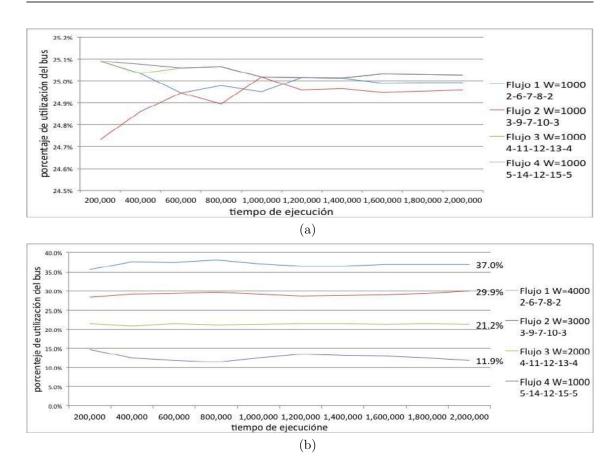

|       | el SDBoC solicita la estadística                                               | 148 |

| 5.14. | Proceso de reconfiguración de los pesos de los cuatro flujos inicia            |     |

|       | 4/3/2/1 luego se reconfigura a $1/2/3/4$ y concluye en $1/1/1/1$               | 149 |

| 5.15. | Proceso de reconfiguración con tres flujos inicia 1/1/1 luego se recon-        |     |

|       | figura a $1/2/2$ y concluye en $1/1/1$                                         | 150 |

|       |                                                                                |     |

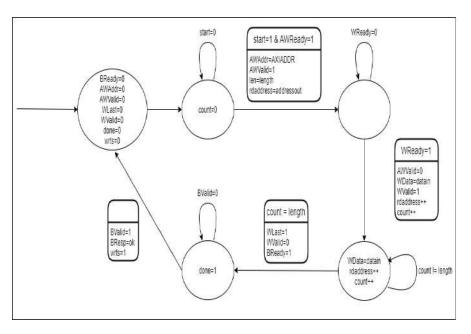

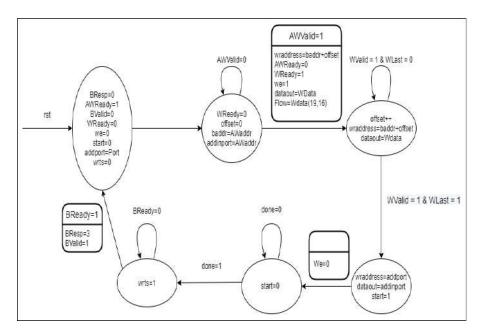

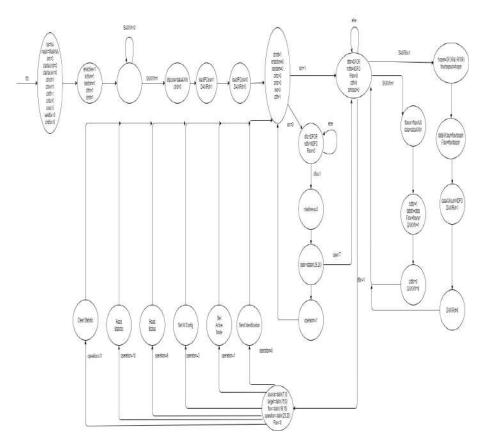

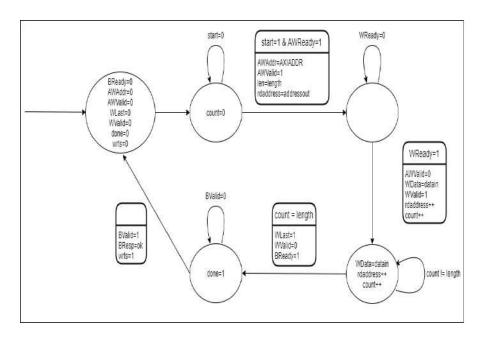

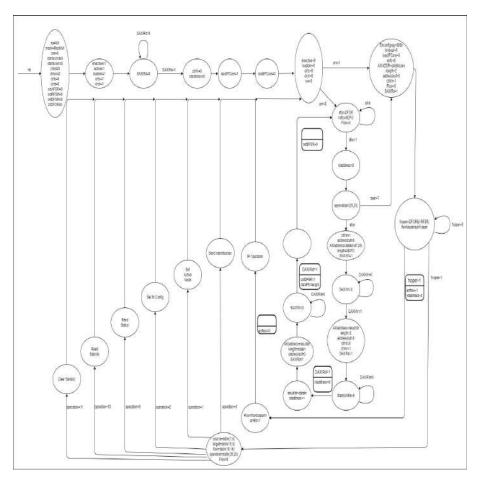

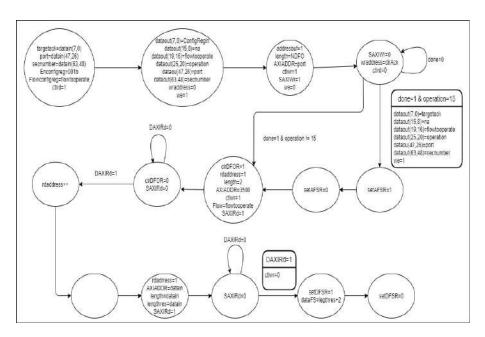

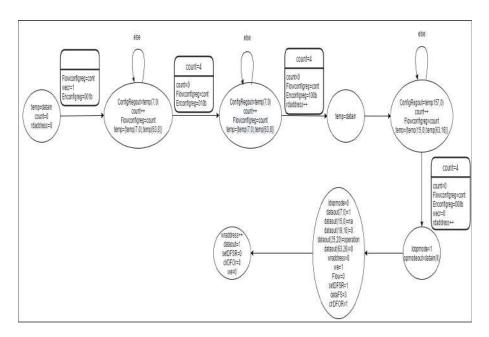

| A.1.  | Diagrama de la MEF de la Interfaz Maestro de escritura AXI-Full en             |     |

|       | un elemento tipo maestro-SDN/maestro                                           | 155 |

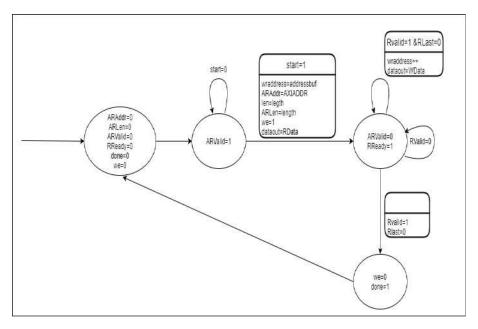

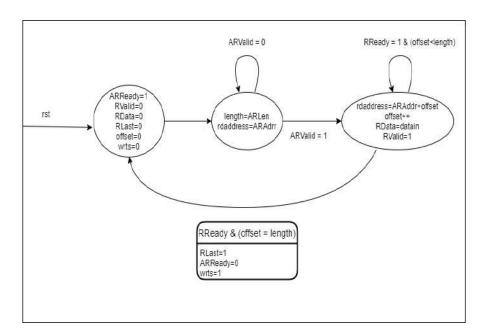

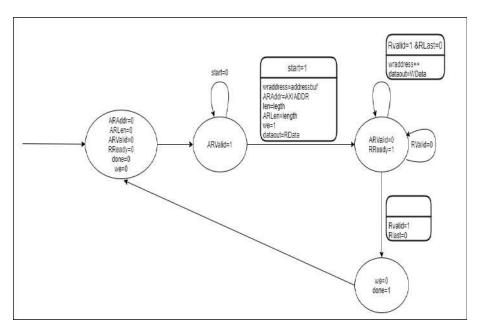

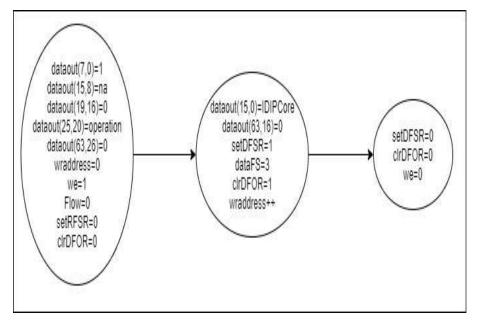

| A.2.  | Diagrama de la MEF de la Interfaz Maestro de lectura AXI-Full en               |     |

|       | un elemento tipo maestro-SDN/maestro                                           | 156 |

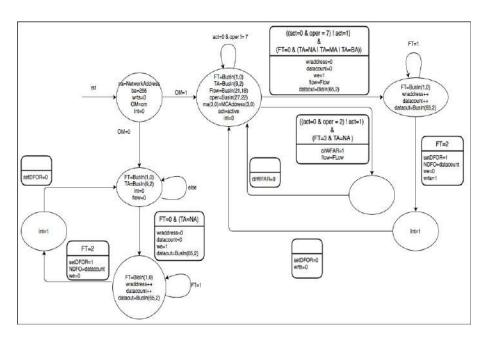

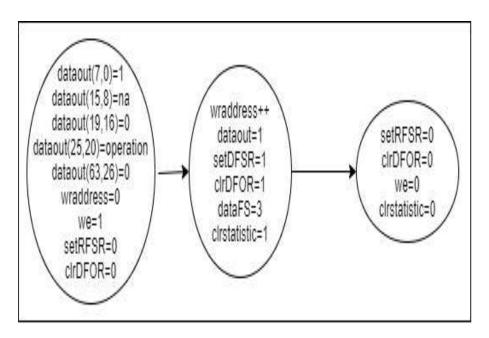

| A.3.  | Diagrama de la MEF de la Interfaz Esclava de escritura AXI-Full en             |     |

|       | un elemento tipo esclavo                                                       | 156 |

| A.4.  | Diagrama de la MEF de la Interfaz Esclava de lectura AXI-Full en               |     |

|       | un elemento tipo esclavo                                                       |     |

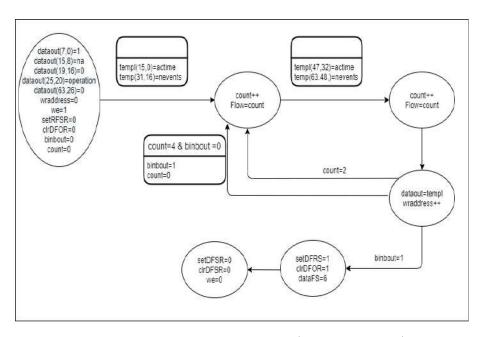

|       | Diagrama de la MEF del Receptor de Red                                         |     |

|       | Diagrama de la MEF del Transmisor de Red                                       | 158 |

| A.7.  | Diagrama de la MEF de la <i>Unidad de Control</i> de la <i>Interfaz de Red</i> |     |

|       | Maestra                                                                        | 159 |

| A.8.  | Diagrama de la MEF de la Interfaz Maestro de escritura AXI-Full en             | 100 |

|       | la Interfaz de Red Esclava                                                     | 160 |

| A.9. Diagrama de la MEF de la Interfaz Maestro de lectura AXI-Full en                     |

|-------------------------------------------------------------------------------------------|

| la Interfaz de Red Esclava                                                                |

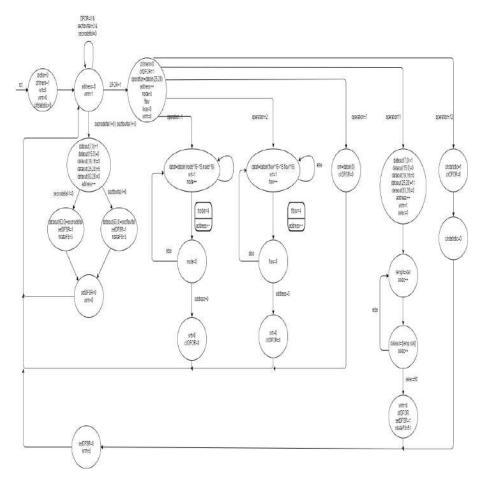

| A.10.Diagrama de la <i>Unidad de Control</i> de la <i>Interfaz de Red Esclava</i> 161     |

| A.11.Diagrama de la <i>Unidad de Control</i> (operación) de la <i>Interfaz de Red</i>     |

| Esclava                                                                                   |

| A.12.Diagrama de la <i>Unidad de Control</i> (envía identificación) de la <i>Interfaz</i> |

| de Red Esclava                                                                            |

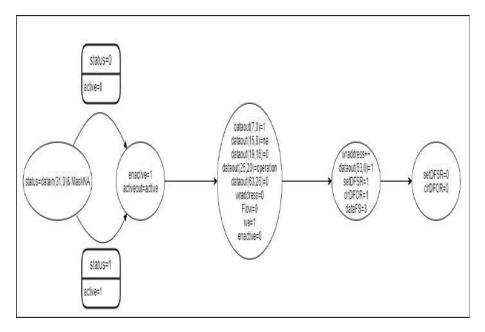

| A.13.Diagrama de la <i>Unidad de Control</i> (activa nodo) de la <i>Interfaz de</i>       |

| <i>Red Esclava</i>                                                                        |

| A.14.Diagrama de la <i>Unidad de Control</i> (leer estado) de la <i>Interfaz de Red</i>   |

| Esclava                                                                                   |

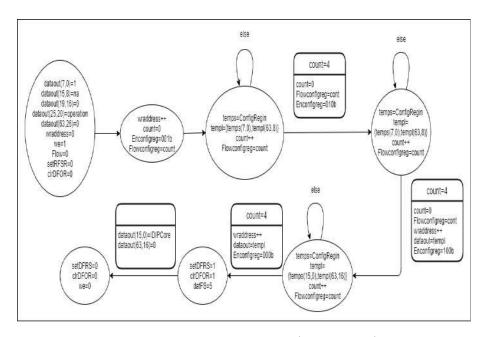

| A.15.Diagrama de la <i>Unidad de Control</i> (configura IR) de la <i>Interfaz de</i>      |

| <i>Red Esclava</i>                                                                        |

| A.16.Diagrama de la <i>Unidad de Control</i> (leer estadística) de la <i>Interfaz de</i>  |

| <i>Red Esclava</i>                                                                        |

| A.17. Diagrama de la <i>Unidad de Control</i> (borrar estadística) de la <i>Interfaz</i>  |

| de Red Esclava                                                                            |

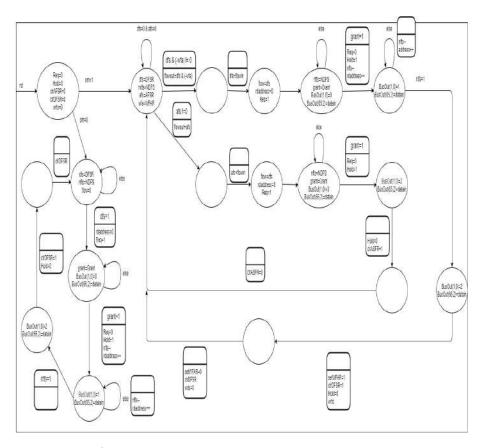

| A.18.Diagrama de la <i>Unidad de Control</i> del <i>Controlador del Bus</i> 166           |

## Índice de tablas

| 3.1.  | Aplicaciones incluidas en la Suite MCSL NoC                              | 69  |

|-------|--------------------------------------------------------------------------|-----|

| 3.2.  | Configuraciones NoC incluidas en la Suite MCSL NoC                       | 69  |

| 3.3.  | Estructura de datos del tráfico generado por la Suite MCSL NoC           | 70  |

| 3.4.  | Estructura de los Archivos de Configuración                              | 74  |

| 3.5.  | Estructura del archivo de dependencias                                   | 77  |

| 4.1.  | Entradas que pueden ser generadas a la tabla de scripts. C=Códi-         |     |

|       | go, B=Byte DM=Dirección Multicast, DR=Dirección de Reenvío,              |     |

|       | P=peso, M=modo de operación                                              | 84  |

| 4.2.  | Estructura de la Tabla con Información de maestros/esclavos              | 86  |

| 4.3.  | Estructura de la Tabla de Flujos                                         | 87  |

| 4.4.  | Estructura del Archivo de Dependencias de un elemento de Procesa-        |     |

|       | miento en el SDBoC                                                       | 88  |

| 4.5.  | Estadística Generada por el SDBoC por Tipo de Elemento. Todos los        |     |

|       | tiempos son acumulados a partir del último $borrado$ de la estadística . | 89  |

| 4.6.  | Consumo de recursos por cada elemento del contenedor AXI-Full para       |     |

|       | un elemento de procesamiento tipo maestro                                | 121 |

| 4.7.  | Consumo de recursos por cada elemento del contenedor AXI-Full para       |     |

|       | un elemento de procesamiento tipo esclavo                                | 121 |

| 4.8.  | Consumo de recursos para una Interfaz de Red Maestra                     | 122 |

| 4.9.  | Consumo de recursos para una Interfaz de Red Esclava                     | 123 |

| 4.10. | Consumo de recursos del Controlador del Bus                              | 123 |

| 5.1.  | Origen de la implementación y significado del peso para cada política    | 134 |

## Siglas

AA Administrador de Aplicaciones. 81

**AAPRR** Asynchronous Adaptive Priority Round-Robin. 42

**ABA** Age-Based Arbitration. 42

**ABL** Age-Based Lottery. 41

**AES** Advanced Encryption Standard. 71

AG Administración General. 83

**AP** Arbitraje Probabilístico. 42

API Application Programming Interface. 4, 45, 48, 50, 52

AR Administrador de Red. 61, 62, 64

**ASIC** Application Specific Integrated Circuits. 14

AT Administración de Tráfico. 85, 88

AWRR Adaptively Weighted Round-Robin. 42

BDAM Base de Datos de Aplicaciones Mapeadas. 87

**C-SDN** Controlador-SDN. 45, 47, 48, 64, 73, 82, 83, 85, 148

**CB** Controlador del Bus. 72, 75, 83, 98, 111–113, 148

CBA Credit-Based Arbitration. 43

CCSPA Credit-Controller Static-Priority Arbitration. 44

CDB Controlador de Datos del Bus. 21

CI Circuito Integrado. 56

CInf Capa de Infraestructura. 60, 91

CR Configuración de Red. 85, 88

CRR Classified Round-Robin. 36

DesR Descubrimiento de Red. 85

**DR** Dispositivos de Reenvío. 47, 97

**dTDMA** dynamic-TDMA. 40

**EP** Elementos de Procesamiento. 17, 19–22, 24–28, 33, 40, 43, 55, 57, 60, 62, 63, 67, 68, 86, 87

ES Elastic Scheduling. 40

**FP** Función de Programación. 85

**FPGA** Field Programmable Gate Array. 21

**FR** Funciones de Red. 59, 82, 85

GALS Globally Asynchronuos, Locally Synchronous. 16

GCT Grafo de Comunicación de Tareas. 18

**HDL** Hardware Description Language. 16

**IN** Interfaz Norte. 49, 52, 60, 82, 83

**IPCore** Intellectual Property Core. 1–4, 6–8, 14–16, 18, 19, 21, 25, 27, 60, 64, 68, 71, 72, 75, 78, 85, 87, 92, 96–98, 102, 106–110, 120, 121, 130, 139, 141–144, 147, 151–153

IR Interfaz de Red. 21, 24, 41, 60–62, 72, 75, 76, 78, 82, 85, 90, 93–99, 101–105, 108–112, 116, 118–120, 144

IRE Interfaz de Red Esclava. 98, 106–108, 110, 123

IRM Interfaz de Red Maestra. 98, 99, 103, 106, 107, 122

**IS** Interfaz Sur. 48, 49, 52, 59, 60, 90, 93

**LTY** Lottery. 34, 37, 38, 41, 43

MEF Máquina de Estados Finitos. 93, 95, 98, 99, 101, 105, 107, 113, 155–160

MOB Modo de Operación del Bus. 83

NDPE Número de Datos Por Enviar. 100

**NoC** Network-on-Chip. 5, 17, 18, 22–25, 27, 41, 42, 54–56, 62, 63, 67, 86, 87

**NofC** Network-of-Chips. 56

PA Plano de Aplicación. 57, 81, 82

PA Plano de Administración. 49

PAR Plano de Administración de la Red. 59, 82, 83, 85, 87

PC Plano de Control. 45, 47, 48, 50, 59, 72, 82, 93

**PCI** Placa de Circuito Impreso. 56

**PD** Priority Division. 40

**PD** Plano de Datos. 45, 48, 50

**PF** Prioridad Fija. 38, 39, 41, 43

PPD Plano de Procesamiento de Datos. 60, 72, 75, 76, 91, 93

**PRD** Plano de Reenvío de Datos. 60, 72, 75, 93, 98

PV Prioridad Variable. 39

**QoS** Quality of Service. 2, 3, 6, 17, 28, 36, 39, 54, 57, 59, 64, 81, 124, 125, 131, 133, 149, 151, 153

RB\_Lottery Real-Time Bandwidth Lottery. 38

RCT Registros de Control de Tráfico. 100

RDPE Registro de Datos Por Enviar. 100, 110

RDPO Registro de Datos Por Operar. 109, 110

RE Recolector de Estadística. 101, 103

REPR Registro de Espera Por Reconocimiento. 107, 110

RGC Registros Generales de Control. 83

**RR** Receptor de Red. 99, 103

**RR** Round-Robin. 30, 31, 36, 38, 39, 41–44

RRPE Registro de Reconocimiento Por Enviar. 110

RT\_lottery Real-Time lottery. 37, 38

RTL Register Transfer Level. 14

RTRE Registro de Tiempo de Recolección de Estadística. 83, 88

**SDBoC** Software Defined Bus-on-Chip. 72, 73, 79–83, 85, 88, 91, 92, 96, 97, 99, 101–103, 105, 106, 109, 111, 118–120, 124, 125, 139, 142–144, 146–149, 152, 153

**SDI** Software Defined Interconnection. 57

**SDN** Software Defined Network. 4–6, 8–10, 12, 13, 44, 45, 47, 49, 52–57, 59, 60, 62–65, 67, 72, 77, 79–81, 85, 88, 91, 118, 120, 124, 125, 139, 146, 151–154

SDNoC Software Defined Network-on-Chip. 55, 61, 62, 153

**SeCMN** Sistema-en-Chip con Múltiples Núcleos. 56

SM Self-Motivated. 39

SO Sistema Operativo. 80, 81, 96

SO Sistema Operativo. 57

**SoC** System-on-Chip. 1–10, 12–23, 27, 28, 41, 44, 53, 55–59, 64, 66, 72, 77–79, 81, 86, 88, 91, 98, 99, 124–127, 131–133, 138, 149, 151, 153, 154

**SOR** Sistema Operativo de Red. 45, 47, 49, 52, 57–60, 72, 82, 83, 124

SR Servicios de Red. 82, 83, 97

SuDO Supervised Debt and Opportunistic. 114, 115

TDMA Time Division Multiple Access. 33, 36, 37, 40

**TF** Tablas de Flujo. 45

TIF Tabla de Información de Flujos. 85

$\mathbf{TR}\,$  Transmisor de Red. 99–101, 104

$\mathbf{TS}$ Tabla de Scripts. 82, 83, 87, 88, 93

UC Unidad de Control. 72

USF Unidad Selectora de Flujo. 100, 101, 103

VCP Verificador de Cumplimiento de Plazos. 37

VR Visor de Red. 83

WRR Weighted Round-Robin. 35, 42, 101

### Glosario

- *Igualdad de Servicio* se refiere a que todos los solicitantes de un servicio que otorga un nodo de la red obtengan la misma proporción de uso del mismo, no importando que tan lejos (lógicamente) se encuentren de él. 42, 57

- Interfaz de Programación de Aplicaciones es un conjunto de definiciones y protocolos que son utilizados para desarrollar e integrar el software de las aplicaciones. 4

- Lenguaje de Transferencia de Registros es un lenguaje de bajo nivel cuya operación se basa en transferir información de un lugar a otro a nivel de registros de hardware. 14

- Lenguajes de Descripción de Hardware es un lenguaje especializado que se utiliza para definir la estructura, diseño y operación de circuitos electrónicos.

16

- *Machine Learning* es una disciplina científica del ámbito de la Inteligencia Artificial que crea sistemas que aprenden automáticamente. 56

- **Mejor Esfuerzo** tipo de transmisión donde los paquetes son conmutados sin ninguna prioridad, no es necesario hardware o mecanismos de control para su traslado. 36, 39

- **Núcleo de Propiedad Intelectual** se refiere a la descripción lógica de un circuito electrónico, comúnmente distribuido como un bloque sintetizable en un lenguaje de descripción de hardware como VHDL o Verilog. 1

- **Procesadores-Software** es un procesador que es totalmente implementado con la lógica programable de un dispositivo lógico programable. 56

- Servicio Garantizado tipo de transmisión donde los paquetes son categorizados basados en tipos de flujo los cuales tienen asignados prioridades. Los flujos con mayor prioridad son utilizados comúnmente para aplicaciones de tiempo real. 36, 39

- **broadcast** es una forma de transmisión de información donde un solo emisor envía información a todos los nodos receptores en su universo. 25, 85, 99

- chiplet componente de hardware, completamente funcional que puede ser agrupado con otros componentes para construir un chip más grande. 56

- end-to-end son servicios que proveen soluciones completas desde su solicitud hasta su entrega, haciendo transparente las capas o procesos por las cuales la solicitud y la respuesta tienen que transitar. 23

- esclavo elemento de procesamiento que responde a las transacciones iniciadas por un maestro en el modelo maestro-esclavo. 21

- **flip-flop** es un dispositivo electrónico capaz de permanecer en uno de dos estados posibles por un tiempo indefinido, utilizado en sistemas digitales para almacenar información. 31

- flit es la unidad de transmisión lógica en un sistema de interconexión. 39, 62

- four-phase dual-rail Es un protocolo handshake de cuatro fases con codificación de doble carril. 42

- hot-spot Un nodo en la red que está siendo intensamente utilizado por los demás nodos de la red en un momento determinado. 42, 64

- *maestro* elemento de procesamiento iniciador de las transacciones en un modelo maestro esclavo. 21

- mapeo de memoria se dice que un dispositivo trabaja bajo este modelo cuando los elementos que lo usan acceden a todas sus funcionalidades como si fueran direcciones de memoria. 7, 8, 93

- *multicast* en este tipo de transmisión los destinatarios de la información es un grupo específico. 99, 103, 106

- *phit* es la unidad de transmisión física del canal de comunicación por donde viajan los paquetes en un sistema de interconexión. 61, 62, 85, 126

- pipeline es una técnica que intenta mantener ocupada cada parte de un procesador, dividiendo las instrucciones en un conjunto de pasos secuenciales ejecutadas por diferentes unidades del procesador. 26

- ruteador también conocido como enrutador o direccionador, proviene del término inglés router. Es un elemento de hardware encargado de interconectar elementos de cómputo que operan en el marco de una red. 42

- scripts Código de programación que contiene comandos que serán ejecutados secuencialmente, utilizados comúnmente para controlar un elemento específico. 15, 58

- **streaming** Se dice que un dispositivo trabaja bajo este modelo cuando por un lado recibe a modo de ráfagas los datos con que va a operar y por otro lado genera una ráfagas con los resultados. 7

- testbench Conjunto de elementos utilizados para probar un diseño, generalmente desarrollado en lenguajes especializados para validación y verificación. 16

- tiempo de ejecución proviene del término en inglés runtime. Indica que un sistema se encuentra en operación. 6, 10, 39–41, 54, 55, 64, 65, 67, 73, 85, 124, 125, 148, 151–153

- unicast en este tipo de transmisión los destinatarios de la información enviada por la red se identifican individualmente. 99

## Capítulo 1

## Introducción

#### 1.1. Antecedentes

En la actualidad, la posibilidad de poder integrar millones de transistores en una oblea de silicio, ha propiciado el surgimiento de arquitecturas que permiten incorporar miles de elementos de procesamiento en un solo circuito. La mayoría de estos elementos son integrados utilizando el modelo de SoC como se menciona en Chen et al. (2017). Basta realizar una simple búsqueda de este tópico en las principales bases de datos científicas para percibir el interés que la comunidad científica y tecnológica ha tenido al respecto. La base de datos IEEEXplore (2020) muestra que en las diferentes revistas y congresos que forman parte de esta asociación, se han publicado cerca de dos mil artículos al respecto en los últimos cinco años. En promedio, un artículo por día. La revista Microprocessors and Microsystems de Elsevier (2020) muestra cerca de quinientos resultados en el mismo periodo, casi cien artículos por año. Este interés es propiciado en parte por una pujante industria electrónica que en el año 2017 tuvo un valor en el mercado de \$444.70 billones de dólares como se indica en el estudio publicado por Foster (2018).

Son varias las ventajas que presentan los SoC por las cuales han tenido una gran aceptación por parte de la comunidad que integra la industria del diseño electrónico. Por un lado, permiten el uso de bloques funcionales de hardware previamente diseñados, probados y verificados denominados Núcleo de Propiedad Intelectual (Intelectual Property Core (IPCore), en inglés). Estos núcleos son capaces de realizar tareas específicas como la compresión de imágenes o cifrado de información. Por otro lado, posibilitan un desarrollo acelerado de los productos de tal modo que pueden tener una presencia más pronta en el mercado. Además, la capacidad de integración que tienen los SoC permite desarrollar sistemas de menor tamaño, menor costo y menor consumo de energía, lo cual los hace muy atractivos para un gran número de aplicaciones que se consumen actualmente.

Sin embargo, la coexistencia de una gran cantidad de elementos de procesamiento al interior de un SoC, genera un nuevo problema: su rendimiento. Actualmente, el rendimiento de un SoC está principalmente determinado por el sistema de interconexión que comunica a los elementos de procesamiento, más que en la capacidad de procesamiento de los mismos. De tal modo que el desarrollo de modelos, arquitecturas e implementaciones de sistemas de interconexión, se ha convertido en una área principal de investigación en los SoC como es señalado por Karkar et al. (2016). Hoy en día, los principales retos que enfrentan los desarrolladores de SoC tienen que ver con tener sistemas de interconexión que: puedan escalar fácilmente; puedan tener la capacidad de controlar su consumo de energía; puedan regular el tráfico que existe en el sistema de interconexión; posibiliten la operación de múltiples aplicaciones en tiempo real; posibiliten que las aplicaciones puedan cumplir con los requerimientos de QoS que se les establecieron –latencia, rendimiento, consumo de energía, etc-. La solución a la mayoría de estos retos se relaciona directamente con los sistemas de interconexión y su administración. De tal modo que la industria, presiona constantemente a la comunidad científica para que se propongan nuevos y mejores modelos de sistemas de interconexión que les permitan mejorar sus condiciones de competencia en el mercado.

#### 1.2. Justificación

Hoy en día, el desarrollo de un proyecto de diseño electrónico se encuentra presionado desde el mismo momento de su concepción. La competencia por presentar en el mercado nuevas soluciones electrónicas crece en intensidad cada día. El ganador es aquel que presente una solución en el menor tiempo y con las mayores prestaciones posibles. Las nuevas metodologías de diseño teniendo esto en mente, promueven prácticas que permiten a los ingenieros responder a estos retos con mayor eficiencia. Una de ellas es el reuso de IPCores. Con esto se evita iniciar un proyecto desde cero y los tiempos de desarrollo se reducen. Para hacer más sencilla la integración de los IPCores es común que éstos se comuniquen por medio de una interfaz estándar que les permite su fácil intercomunicación. Además, hoy en día el proceso de diseño se enfoca desde su primera etapa en cumplir con los requerimientos de operación que le fueron establecidos al producto. Cuando se realiza la implementación hardware de un algoritmo ésta se desarrolla teniendo en mente satisfacer los requerimientos que tienen que ver principalmente con: rendimiento, la implementación hardware debe tener la capacidad de procesar una cierta cantidad de datos por unidad de tiempo; consumo de energía, el sistema no debe de sobrepasar una cantidad de consumo especificado; tamaño, el circuito no debe exceder una cierta cantidad de área especificada; latencia, el tiempo para que un dato sea procesado no debe exceder un límite establecido. Este último requerimiento es especialmente crítico para sistemas que operan en tiempo real. Lo anterior sitúa a los equipos de diseño en una aparente contradicción, ya que para cumplir con los requerimientos de diseño – generalmente ambiciosos– es necesario realizar implementaciones *ad hoc* lo que impide en principio el reuso de IPCores implicando tiempos de desarrollo mayores.

Con la finalidad de poder lograr tener una buena relación entre tiempo de desarrollo y cumplir con los requerimientos de operación, se han desarrollado al interior de los SoC, sistemas de interconexión de los IPCores que al mismo tiempo que permiten su fácil integración, posibilitan hasta cierto punto cumplir con los requerimientos de QoS que se le imponen al producto. Sin embargo, aunque los sistemas de interconexión se han convertido de facto en la tecnología de interconexión de elementos de procesamiento al interior de los SoC, diferentes autores apuntan que hoy en día, el principal cuello de botella que limita el rendimiento de un SoC, se encuentra principalmente en el sistema de interconexión más que en el rendimiento particular de cada IPCore Poletti et al. (2003); Ahmed et al. (2017); Ben Slimane et al. (2017); Dally and Towles (2003); Benini and Bertozzi (2005). Ante esto la comunidad científica que estudia los problemas relacionados con esta área, ha dirigido sus esfuerzos a estudiar y proveer sistemas de interconexión que coadyuven a incrementar el rendimiento de los SoC. Con esto, intentan mejorar las prestaciones de las aplicaciones para que puedan cumplir con los requerimientos de diseño establecidos.

Al convertirse los sistemas de interconexión en un elemento clave para que un SoC mejore sus prestaciones, existen varias características que son deseables que estos tengan:

- Flexible: Aunque la infraestructura de un sistema de interconexión se construya sobre una topología específica, el sistema de interconexión debe de proveer la capacidad de poder operar lógicamente bajo diferentes topologías.

- Reconfigurable: El sistema de interconexión debe de tener la capacidad de modificar sus parámetros de operación en cualquier momento. Debe de ser capaz de modificar su topología; establecer o eliminar flujos; cambiar políticas de arbitraje; debe de tener la capacidad de agregar o eliminar elementos de procesamiento del sistema de interconexión; etc.

- Escalable: Debe permitir modificar las dimensiones del sistema de interconexión sin impactar el rendimiento de las aplicaciones.

- Reutilizable: El sistema de interconexión debe de poder integrarse fácilmente a diferentes entornos de SoC.

- Fácil Administración: La lógica que permita realizar las anteriores características no debe de ser mayor que la misma infraestructura del sistema de interconexión.

Una alternativa de solución para la implementación y gestión de los sistemas de interconexión, que ha surgido en los últimos años, tiene su origen en el modelo SDN que es utilizado para la administración de redes de comunicación de datos. Este paradigma le ha provisto a la industria de las redes de comunicación de una herramienta que le posibilita un mejor control de sus sistemas. Un sistema que tuvo en sus inicios un fin académico McKeown et al. (2008), hoy es utilizado por algunos de los grandes competidores en el área de redes de comunicaciones como son Cisco (2020) y ONF (2014), para proveer herramientas que les permitan a sus usuarios: simplificar operaciones; desarrollar redes programables; centralizar y automatizar las configuraciones; implementar más rápido nuevas aplicaciones aprovechando el uso de una *Interfaz de Programación de Aplicaciones* (Application Programming Interface (API), en inglés) abierta.

Algunos autores han tomado los conceptos principales del paradigma SDN para aplicarlos en los sistemas de interconexión de los SoC. La separación del plano de retransmisión de datos, del plano de control que promueve SDN, encaja muy bien en los sistemas de interconexión tipo red, que son una tendencia generalizada en la comunidad desarrolladora de SoC. Este paradigma, posibilita crear estructuras de administración y control definidas por software, sin necesidad de hacer cambios en el hardware del sistema de interconexión. Además, por medio de la construcción de interfaces de comunicación estandarizadas se posibilita el reuso de los IPCores con lo que el tiempo de arribo al mercado de nuevas aplicaciones es más corto. Los problemas referentes a mapeo de aplicaciones, ruteo de paquetes, administración de la energía, programación, son ahora resueltos desde capas superiores de la red vía software. La aplicación de los conceptos SDN en los SoC resulta muy prometedora, sus principales objetivos: escalabilidad, control de tráfico, gestión dinámica del ancho de banda, gestión centralizada de los recursos, supervisión de recursos y usuarios, generación de estadística para la toma de decisiones, seguridad en las comunicaciones, son también objetivos que se desean obtener en el entorno de un sistema de interconexión para un SoC. Sin embargo, la tarea de desarrollar sistemas de interconexión basados en SDN apenas comienza, hay una gran cantidad de trabajo que realizar. Es necesario proponer modelos, arquitecturas, protocolos, interfaces, infraestructura que permitan alcanzar estos objetivos.

Los sistemas de interconexión basados en bus han estado vigentes por mucho años. Es la base de algunos sistemas de interconexión utilizados por varios de los principales competidores en la industria ARM (2010), Intel (2020a). Sin embargo, a pesar de que han sido ampliamente utilizados, existen elementos en su comportamiento que no han sido totalmente estudiados. Por ejemplo, las políticas de arbitraje que actualmente se utilizan en la mayoría de las implementaciones de este tipo de sistemas de interconexión, se ocupan más en asegurar un acceso justo al sistema, que en regular el uso del bus de acuerdo a las necesidades particulares de un ele-

mento de procesamiento. Teniendo en cuenta que esto es una característica deseable de un sistema de interconexión considero que es importante estudiar nuevas políticas de arbitraje que permitan hacer un uso diferenciado de un recurso compartido. También es deseable presentar mayor evidencia del comportamiento de las políticas de arbitraje en escenarios que son cada día mas comunes y que han sido poco estudiados como aquellos escenarios donde se ejecutan simultáneamente aplicaciones heterogéneas con dependencia en la ejecución de sus tareas.

Por lo anteriormente planteado, se decidió realizar un estudio sobre la aplicación de los conceptos del modelo SDN en un sistema de interconexión para un SoC. Poniendo atención principalmente en las características que deben de tener los elementos que forman parte de la capa de infraestructura — hardware— del sistema de interconexión tipo bus. Además, en el estudio se deberán mostrar los principales mecanismos de comunicación con las capas superiores del modelo seleccionado. Desde mi punto de vista, es útil realizar un estudio que proporcione evidencia que permita identificar las ventajas del uso del modelo SDN en un SoC en general y, en un sistema de interconexión tipo bus en lo particular.

#### 1.3. Alcances

El estudio aquí realizado toma como marco de referencia la arquitectura para sistemas de interconexión bajo el enfoque SDN propuesta por Sandoval-Arechiga et al. (2015). El estudio se centra principalmente en el diseño de la infraestructura – hardware – necesaria para implementar un sistema de interconexión definido por software. En este trabajo se hace especial énfasis en las características de los elementos encargados de la transmisión de los datos. La forma en que opera la infraestructura es regida por elementos en las capas superiores de la arquitectura – software –. El estudio no implementa en su totalidad estas capas, pero sí proporciona las principales rutinas de servicio que se deben de ofrecer para que la infraestructura pueda operar en el modo SDN. Los algoritmos de optimización que permiten mejorar las prestaciones de uno o varios elementos del sistema se encuentran fuera del alcance de este estudio.

Tradicionalmente los sistemas de interconexión en un SoC se han dividido en tres categorías: sistemas de interconexión basados en bus, sistemas de interconexión tipo crossbar y las denominadas Redes en Chip (Network-on-Chip (NoC), en inglés). Varios autores han apuntado que estos sistemas de interconexión más que competir entre sí, se complementan Ben Achballah et al. (2017); Bjerregaard and Mahadevan (2006). En este estudio se ha decidido centrar la investigación en los sistemas de interconexión basados en bus por las siguientes razones:

■ En la actualidad existen muchas aplicaciones que tienen como base el sistema

de interconexión basado en bus. Estas aplicaciones pueden verse beneficiadas con las posibilidades que ofrece una gestión basada en SDN como: la posibilidad de operar por medio de flujos; la posibilidad de asignar un ancho de banda específico a una aplicación en el sistema; control energético del sistema; reconfiguración de flujos, aplicaciones, y de los parámetros de operacion de los IPCores en tiempo de ejecución; conocer la estadística del sistema de interconexión para la toma de decisiones, entre otros.

- Algunos elementos del sistema de interconexión basado en bus son comunes a los otros sistemas de interconexión, de tal modo que los resultados aquí obtenidos pueden extrapolarse a los otros sistemas de interconexión.

- Los principios básicos de funcionamiento del sistema de interconexión basado en bus permiten aislar puntualmente problemas que se presentan en los sistemas de interconexión. Uno de estos problemas, que causa el principal cuello de botella en un SoC, es el uso de recursos compartidos. Hoy en día, no es suficiente tener un uso justo del bus, sino que hay que racionalizarlo de acuerdo a las necesidades de los usuarios aplicaciones —. La evaluación de árbitros y sistemas de apoyo que permitan el uso racional de estos recursos es parte fundamental de este estudio y el sistema de interconexión tipo bus es el medio ideal para su estudio.

En este trabajo se presentarán las características de los elementos de la infraestructura de un sistema de interconexión basado en bus bajo el paradigma SDN. Se propondrá una arquitectura que permita el transporte de los datos que se encuentre aislada de los elementos que procesan los datos. Se presentará una estrategia para la integración de los elementos de procesamiento por medio de una interfaz bien conocida procurando el reuso de los IPCores. Se mostrará un estudio de los principales sistemas de arbitraje utilizados en SoC y se hará una propuesta de una política que permite el uso proporcional de recursos compartidos. Además, se definirán las principales rutinas de servicios que deben estar integradas en los planos superiores de la arquitectura de interconexión definida por software.

#### 1.4. Planteamiento del problema

Una de las principales medidas de QoS que se le impone a una aplicación es el rendimiento. Es decir, una aplicación debe de cumplir con una cierta cuota de procesamiento en una unidad de tiempo. Esta medida puede resultar difícil de obtener cuando en un SoC se ejecutan simultáneamente diferentes aplicaciones que compiten por el uso de un recurso – sistema de interconexión, controlador de memoria, etc.—. Cuando esto sucede es común que una aplicación, la que genera las transacciones

más grandes, acapare el uso del recurso compartido. Lo anterior es debido principalmente a que, los árbitros que tradicionalmente se han encargado de permitir el acceso al recurso, se rigen bajo una política que se enfoca más, en permitir un acceso justo al recurso, que en controlar el tiempo de uso del mismo. En los actuales SoC, donde se ejecutan aplicaciones muy diversas, es deseable que durante ciertos periodos una de las aplicaciones pueda acceder al recurso de manera preferencial. Pero en otro periodo es necesario que la preferencia la tenga otra aplicación. Lo anterior plantea la necesidad de contar con un sistema de arbitraje, que no solo controle el acceso a un recurso compartido, sino que adicionalmente regule el tiempo que este puede ser usado. Además, la regulación debe de poder llevarse a cabo sin sacrificar el rendimiento global del sistema.

Por otro lado, una de las principales necesidades de la industria electrónica, es poder llevar productos al mercado en el menor tiempo posible. Por esto, durante mucho tiempo se ha insistido en la posibilidad del reuso de los IPCores, ya sean propios o de terceros. En este sentido se han tenido buenos resultados al respecto debido a que ya existen interfaces de comunicación bien definidas en el mercado. Sin embargo, las interfaces trabajan principalmente bajo el modelo de mapeo de memoria o de streaming. Estas interfaces no son lo suficientemente flexibles y escalables como lo requieren los SoC en la actualidad. En este sentido con la finalidad por un lado de poder aprovechar la gran cantidad de IPCores que ya existen en el mercado; y por otro lado integrarlos a un sistema de interconexión más flexible, es necesario el desarrollo de circuitos convertidores de protocolo que permitan a los IPCores existentes, integrarse fácil y rápidamente en un sistema de interconexión de conmutación de paquetes. En este caso, basado en una topología bus.

Existen muchas aplicaciones cuyo resultado se deriva de efectuar una serie de transformaciones en forma secuencial a un conjunto de datos. Es decir, los datos que son generados por una fuente "fluyen río abajo" a un primer IPCore que les transforma. Los datos, resultado de esta transformación continúan su flujo "río abajo" a un segundo IPCore para continuar su procesamiento, y así sucesivamente hasta que los datos terminan su transformación. Cuando este tipo de aplicaciones son implementadas en un SoC con un sistema de interconexión tipo bus tradicional, existe un overhead en la transmisión de los datos. Esto es debido a que el maestro encargado del proceso envía los datos al primer IPCore en el flujo y espera por el resultado de esta transformación. Posteriormente envía los datos que recibió transformados al segundo IPCore para continuar su transformación y vuelve a esperar por el resultado antes de transmitirlo nuevamente. Este comportamiento implica el transporte de los mismos datos en un par de ocasiones por el bus. Lo que además de retardar la operación de los datos, genera un mayor uso del bus. Este comportamiento no solo impacta en el rendimiento de la aplicación, ya que está generando tráfico redundante, sino que en general afecta el tráfico de las demás aplicaciones, perjudicando el rendimiento global del sistema. Por lo anteriormente planteado es deseable el desarrollo de una nueva infraestructura para un sistema de interconexión tipo bus que permita mayor flexibilidad en el transporte de los datos.

La seguridad es un elemento que hoy en día es parte fundamental de cualquier sistema de comunicación. Un sistema de interconexión en un SoC no está exento de problemas de intrusión, por lo que se deben proveer mecanismos de seguridad que controlen el acceso al mismo. Es decir, debe de ser capaz de permitir que en el sistema solo viajen paquetes pertenecientes a nodos y/o flujos autorizados. Además, debe de ser capaz alertar a los elementos de gestión del intento de intrusión.

Para dar solución a los problemas anteriormente planteados se propone el diseño e implementación de una arquitectura de un sistema de interconexión basada en los conceptos de SDN que sea: flexible, reconfigurable, reusable, segura y de fácil administración, características que se esperan de los actuales sistemas de interconexión.

#### 1.5. Objetivos

El objetivo principal de esta investigación es: el desarrollo de la infraestructura para un sistema de interconexión tipo bus que opere bajo el paradigma SDN en un SoC, de tal modo que se puedan incrementar las prestaciones otorgadas por los modelos tradicionales de interconexión tipo bus.

Los objetivos específicos del estudio son:

- Diseñar una política de arbitraje que permita el uso diferenciado del bus poniendo especial atención en escenarios donde se ejecuten simultáneamente aplicaciones con dependencia de tareas.

- Diseñar un sistema que permita integrar los IPCores con interfaces con mapeo de memoria, a un sistema de interconexión basado en el transporte de paquetes.

- Diseñar la infraestructura necesaria para que un sistema de interconexión tipo bus pueda trabajar bajo el modelo SDN.

- Identificar y detallar las capacidades que deben de tener los controladores de software que deben de existir en los planos superiores de la arquitectura SDN para que exista una gestión adecuada de los recursos de hardware del sistema.

#### 1.6. Metodología

Para el desarrollo de este estudio se siguió la siguiente metodología:

- 1. Se realizó un estudio detallado del estado del arte respecto al tópico de sistemas de interconexión en SoC. Se detectaron qué ventajas y/o desventajas se presentan en las propuestas encontradas.

- 2. Se detectaron los principales problemas que presentan los sistemas de interconexión utilizados en un entorno SoC.

- 3. Con el objetivo de mejorar las prestaciones de los sistemas de interconexión en un SoC, se estudiaron nuevos modelos de gestión y se identificó cómo estos pueden impactar en la mejora de dichas prestaciones. Se identificó una arquitectura basada en SDN para sistemas de interconexión, la cual fue tomada como ancla para el desarrollo de los elementos de la capa de infraestructura de este trabajo. Se identificó qué elementos de la arquitectura pueden ser aplicados al sistema de interconexión tipo bus con la finalidad de mejorar el rendimiento general del sistema y aumentar sus prestaciones, con respecto a un sistema de interconexión tipo bus tradicional.

- 4. Se identificaron un conjunto de escenarios de uso común en SoC sobre los cuales los modelos de sistemas de interconexión tipo bus tradicionales limitan su rendimiento. Además se identificó qué elementos de la infraestructura son los que limitan el rendimiento.

- 5. Se diseñó e implementó una arquitectura hardware de un sistema de interconexión basado en *bus* tradicional. Esta arquitectura incluye: controlador del bus, árbitro, interfaces de red, maestros, esclavos y acopladores.

- 6. Uno de los principales problemas que enfrentan los diferentes tipos de sistemas de interconexión, es el poder permitir el uso diferenciado de un recurso compartido a diferentes elementos de procesamiento que lo requieran. Para poder conocer en qué grado diferentes políticas de arbitraje pueden resolver este problema, se desarrollaron e implementaron estas políticas, y se integraron al sistema de interconexión tipo bus construido para su evaluación. Del conjunto de simulaciones realizadas se efectuó un estudio comparativo de su comportamiento.

- 7. Se desarrolló y probó una nueva política de arbitraje que permite el uso diferenciado del bus y que presenta el mejor comportamiento cuando el sistema de interconexión se encuentra ejecutando múltiples aplicaciones con tareas dependientes.

- 8. En base a las características detectadas en el modelo de referencia, las cuales pueden contribuir a proveer un mejor comportamiento del sistema de interconexión tipo bus, se procedió a modificar la arquitectura hardware del sistema

de interconexión. Esta infraestructura involucra los elementos necesarios para proveer un control del bus bajo una filosofía SDN. Además se detectaron y desarrollaron los controladores de software que habilitan el uso de esta infraestructura.

9. Se procedió a evaluar el comportamiento de la arquitectura desarrollada y se contrastó con la arquitectura tradicional. Se evaluó que la nueva arquitectura tenga las posibilidades de trabajar bajo el modo de flujos de datos, que tenga la capacidad de reconfiguración en tiempo de ejecución, que permita diferentes tipos de operación, que permita conocer el estado de cada uno de los elementos en cualquier momento, y que genere estadística que pueda ser consultada en cualquier momento por el controlador del sistema, para que en caso de ser necesario, se pueda modificar el comportamiento del sistema de interconexión.

#### 1.7. Contribuciones

Las principales contribuciones de este trabajo son:

- La realización de un estudio, con precisión de ciclo de reloj, del comportamiento de las principales políticas de arbitraje utilizadas en los sistemas de interconexión para SoC.

- La propuesta de una nueva política de arbitraje basada en presupuesto que permite el uso diferenciado de un recurso compartido.

- El desarrollo de una infraestructura de hardware para que un sistema de interconexión tipo bus pueda ser gestionado bajo el modelo SDN.

- Se presenta evidencia que muestra que las prestaciones de un sistema de interconexión tipo bus pueden ser incrementadas cuando éste trabaja bajo el paradigma SDN.

- Se presenta evidencia que muestra que los sistemas de interconexión para SoC basados en SDN permiten cumplir con las características deseables de los sistemas de interconexión actuales.

#### 1.8. Publicaciones Científicas Relacionadas

Parte de los resultados que se han derivado del proceso de investigación y que se exponen en esta Tesis Doctoral han aparecido previamente en algunas publicaciones:

- Gómez-Rodríguez J.R., Sandoval-Arechiga R., Ibarra-Delgado S., Rodriguez-Abdala V.I., Vazquez-Avila J.L. and Parra-Michel R. A Survey of Software-Defined Networks-on-Chip: Motivations, Challenges and Opportunities. *Micromachines* 2021, 12(2), 183.

- Ibarra-Delgado S., Sandoval-Arechiga R., Gómez-Rodríguez J.R., Ortíz-López M. and Brox M. A Bandwidth Control Arbitration for SoC Interconnections Performing Applications with Task Dependencies. *Micromachines* 2020, 11(12), 1063.

- Ibarra-Delgado S., Sandoval-Arechiga R., Brox M. and Ortíz-López M. Throughput Unfairness in Fair Arbitration Interconnection-Buses for Aerospace Embedded Systems. IEEE Latin America Transactions 2020, 18(9), 1606

- Ibarra-Delgado S., Sandoval-Arechiga R., Brox M., Ortíz-López M. Arquitecturas Definidas por Software, una alternativa flexible para la interconexión de Sistemas en Chip. Libro de Actas XXVI Seminario Anual de Automática, Electrónica Industrial e Instrumentación, Córdoba, España, 2019, pp. 108-113.

- Ibarra-Delgado S., Sandoval-Arechiga R., Brox M., Ortíz-López M. Software defined network controller: A neat solution administration for reconfigurable multi-core NoC. *International Conference on ReConfigurable Computing and FPGAs*, Cancun, México, 2017, pp. 1-4.

- Sandoval-Arechiga R., Ibarra-Delgado S., Flores-Troncoso J., A Software Defined Interconnection Architecture for Systems on Chip. Difu100ci@ Revista de Ingeniería y Tecnología 2017, 10(2).

- Sandoval-Arechiga R., Vazquez-Avila J.L., Parra-Michel R., Flores-Troncoso J., Ibarra-Delgado S. Software Defined Networks-on-Chip for multy/many-core systems: A performance evaluation, *ACM/IEEE Symposium on Architectures for Networking and Communications Systems*, Santa Clara, USA, 2016, pp. 129-130.

- Sandoval-Arechiga R., Vazquez-Avila J.L., Parra-Michel R., Flores-Troncoso J., Ibarra-Delgado S. Shifting the Network-on-Chip Paradigm towards a Software Defined Network Architectura. *International Conference on Computational Science and Computational Intelligence*, Las Vegas, USA, 2015, pp.869-870.

### 1.9. Estructura general de la tesis

El resto del presente documento está estructurado de la siguiente forma: en el capítulo dos, se muestra el marco teórico que presenta los principales conceptos que

deben de ser tomados en cuenta en un sistema de interconexión para un SoC. Al mismo tiempo se integra un estudio de los principales trabajos que la comunidad científica ha presentado al respecto. En el capítulo tres se presenta el modelo del sistema, donde se mencionan las herramientas, modelos, topologías y suposiciones hechas para el desarrollo del estudio. La arquitectura de la infraestructura de interconexión propuesta con un enfoque SDN es presentada en el capítulo cuatro. Los resultados obtenidos así como la discusión de los mismos son presentadas en el capítulo cinco. Finalmente las conclusiones de este estudio se presentan en el capítulo seis.

## Capítulo 2

## Marco Teórico

La industria informática y electrónica busca constantemente dar soluciones a problemas complejos con aplicaciones que se encuentren integradas en circuitos cada vez más pequeños, baratos y que consumen menos energía. El desarrollo de soluciones basadas en SoC es una alternativa común hoy en día. Sin embargo, los retos a los que se enfrentan los desarrolladores son diferentes y variados. Uno de ellos, quizá el más importante, tiene que ver con el sistema de intercomunicación que existe entre los elementos de procesamiento que hay en el interior de un SoC. Antes de ofrecer una alternativa de solución a este problema, en este capítulo se describirán algunos conceptos fundamentales de los SoC y de sus sistemas de interconexión. Inicialmente se describirán las principales características de los SoC. Posteriormente se describirán los principales tipos de sistemas de interconexión utilizados en los SoC así como sus ventajas y desventajas. A continuación se presentará la necesidad de realizar arbitraje y los principales tipos de árbitros que se utilizan en los SoC. El trabajo aquí presentado toma como marco de referencia el paradigma SDN, los principales conceptos de este modelo son presentados en este capítulo. Enseguida se muestra el enfoque SDN aplicado a los SoC. Se indican las principales diferencias con los sistemas de interconexión tradicionales y se delinean las características de la infraestructura necesaria para implementar sistemas de interconexión con el enfoque SDN. El desarrollo de SoC está ligado al cumplimiento de requerimientos de operación que comúnmente son englobados en lo que se denomina Calidad de Servicio. En este capítulo se describen las principales medidas que se usan en este sentido. Finalmente, se menciona la necesidad de mapear aplicaciones sobre un conjunto de procesadores en un SoC.

#### 2.1. Sistemas-en-Chip

Una constante que se observa en la industria del diseño electrónico, es su capacidad ininterrumpida de crecimiento. La cantidad de elementos electrónicos que pueden ser integrados en una sola pastilla es cada día mayor. Esto ha permitido no solo contar con circuitos integrados que puedan realizar operaciones más complejas, sino integrar, en un solo chip, múltiples elementos de procesamiento, que en la industria del diseño electrónico se les conoce como SoC. Lee and Bergmann (2003), señalan que inicialmente esta tecnología se convirtió en la metodología predominante para el diseño de los denominados Circuitos Integrados para Aplicaciones Específicas (Application Specific Integrated Circuits (ASIC), en inglés). Sin embargo, hoy en día resulta también común encontrarlos en sistemas en chip reconfigurables como el denominado Zynq-7000, de Xilinx (2018) o el AGILEX, de Intel (2020b). Cuando a los SoC se les pudieron integrar cientos de elementos de procesamiento, fue necesario que a éstos se les adicionaran nuevas capacidades, las cuales permitan que la industria provea productos con mejores prestaciones, al mismo tiempo que estén en el mercado en el menor tiempo posible. Dos de las características más importantes que se busca en la industria hoy día, con respecto a los SoC, son: la reusabilidad y su capacidad de integración.

#### 2.1.1. Reusabilidad

Desde hace más de una década, algunos autores, Saleh et al. (2006); Keating and Bricaud (2012), han señalado que una de las principales características que se busca que tengan los SoC es la reusabilidad. Es decir que los denominados IPCores, puedan ser utilizados en diferentes proyectos, en diferentes momentos, por diferentes equipos y por diferentes compañías. Esto es posible hoy en día porque los IPCores son implementados en base a código desarrollado en un Lenguaje de Transferencia de Registros (Register Transfer Level (RTL), en inglés) que puede ser transportado a cualquier tecnología. Los IPCores pueden ser propietarios o provenir de terceros. Existe una gran variedad de IPCores: procesadores de propósito general, procesadores de propósito específico, controladores de memoria, controladores de buses, interfaces, etc. Y son utilizados en diferentes áreas: comunicaciones, procesamiento de imagen, procesamiento de vídeo; y por varios sectores: defensa, tecnología aeroespacial, automotriz, medicina, industria, entre otras. Cada día son más las aplicaciones que son puestas al mercado en cada una de las áreas anteriormente mencionadas y existe mucha presión por parte del mercado para obtener más rápido, nuevos y mejores productos. Por lo que nuevas técnicas deben de ser utilizadas para el desarrollo de productos. Algunas de los razones por las cuales se considera necesario la reusabilidad de los IPCores son identificadas por Keating and Bricaud (2012):

- Presiones por reducir el tiempo de salida al mercado de los productos.

- La calidad de los resultados, en términos del rendimiento en área y energía, son claves para el éxito en el mercado.

- El incremento en la complejidad del chip hace el proceso de verificación más difícil.

- La operación a nivel *submicron* hace más difícil la sincronización.

- Los equipos de desarrollo tienen diferentes niveles y áreas de *expertise*, y a veces se encuentran dispersos.

- Los diseños basados en SoC frecuentemente incluyen procesadores embebidos, y por lo tanto un componente de software significativo que conduce a desafíos adicionales de metodología, proceso y organización.

Sin embargo, es importante mencionar que el reuso de componentes implica una metodología de diseño con cambios significativos respecto a las metodologías tradicionales. Según Keating and Bricaud (2012) esta nueva metodología debe de estar basada en los siguientes principios:

- Creación en todas las etapas del desarrollo, desde las especificaciones hasta la integración en el silicio, con el pensamiento que el diseño puede ser modificado y reusado en otros proyectos y por otros equipos de diseño.

- El uso de herramientas y procesos que capturen la información de diseño de una forma consistente y fácil de entender.

- El uso de herramientas y procesos que hagan fácil la integración de módulos dentro de un diseño, cuando el diseñador original no es parte del proyecto.

Además de las técnicas tradicionales de diseño: buena documentación, buen código, comentarios minuciosos, buenos ambientes de verificación y el desarrollo de *scripts* robustos, existen requerimientos adicionales que el IPCore debe de cumplir cuando es diseñado bajo el modelo de reusabilidad: