Programa de doctorado: Computación Avanzada, Energía y Plasmas

Optimización de Algoritmos Científicos en Sistemas Heterogéneos y Aceleradores para Computación de Altas Prestaciones

Optimization of Scientific Algorithms in Heterogeneous Systems and Accelerators for High Performance Computing

# Directores:

Dr. Juan Gómez Luna Dr. Rafael Medina Carnicer

*Autor:* D. Antonio Fuentes Alventosa

> *Fecha de depósito:* Enero de 2023

# AUTOR: Antonio Fuentes Alventosa

© Edita: UCOPress. 2023 Campus de Rabanales Ctra. Nacional IV, Km. 396 A 14071 Córdoba

https://www.uco.es/ucopress/index.php/es/ ucopress@uco.es

### TÍTULO DE LA TESIS:

Optimización de Algoritmos Científicos en Sistemas Heterogéneos y Aceleradores para Computación de Altas Prestaciones

**DOCTORANDO/A:** Antonio Fuentes Alventosa

#### INFORME RAZONADO DEL/DE LOS DIRECTOR/ES DE LA TESIS

(se hará mención a la evolución y desarrollo de la tesis, así como a trabajos y publicaciones derivados de la misma)

Consideramos que el doctorando ha alcanzado los objetivos de la tesis doctoral con la paralelización de tres importantes algoritmos científicos utilizando procesadores gráficos (GPU).

Productos del trabajo son tres artículos en revistas indexadas JCR, que le permiten presentar la tesis doctoral por compendio de artículos:

- Fuentes-Alventosa, A., Gómez-Luna, J., González-Linares, J. M., Guil, N., & Medina-Carnicer, R. (2022). CAVLCU: an efficient GPU-based implementation of CAVLC. The Journal of Supercomputing, 78(6), 7556-7590.

- Journal Impact Factor (2021): 2.557 (Q2).

- Category: Computer Science, Theory & Methods.

- Fuentes-Alventosa, A., Gómez-Luna, J., & Medina-Carnicer, R. (2022). GUD-Canny: A real-time GPU-based unsupervised and distributed Canny edge detector. Journal of Real-Time Image Processing, 19(3), 591-605.

- Journal Impact Factor (2021): 2.293 (Q3).

- Category: Computer Science, Artificial Intelligence.

- Fuentes-Alventosa, A., Gómez-Luna, J., & Medina-Carnicer, R. (2022). GVLE: a highly optimized GPU-based implementation of variable-length encoding. The Journal of Supercomputing, 1-28.

- Journal Impact Factor (2021): 2.557 (Q2).

- Category: Computer Science, Theory & Methods.

Por todo ello, se autoriza la presentación de la tesis doctoral.

Córdoba, 11 de enero de 2023

Firma de los directores

Fdo.: Juan Gómez Luna

Fdo.: Rafael Medina Carnicer

# Resumen

Actualmente, la computación de propósito general en GPU es uno de los pilares básicos de la computación de alto rendimiento. Aunque existen cientos de aplicaciones aceleradas en GPU, aún hay algoritmos científicos poco estudiados. Por ello, la motivación de esta tesis ha sido investigar la posibilidad de acelerar significativamente en GPU un conjunto de algoritmos pertenecientes a este grupo.

En primer lugar, se ha obtenido una implementación optimizada del algoritmo de compresión de vídeo e imagen CAVLC (Context-Adaptive Variable Length Encoding), que es el método entrópico más usado en el estándar de codificación de vídeo H.264. La aceleración respecto a la mejor implementación anterior está entre 2.5x y 5.4x. Esta solución puede aprovecharse como el componente entrópico de codificadores H.264 software, y utilizarse en sistemas de compresión de vídeo e imagen en formatos distintos a H.264, como imágenes médicas.

En segundo lugar, se ha desarrollado GUD-Canny, un detector de bordes de Canny no supervisado y distribuido. El sistema resuelve las principales limitaciones de las implementaciones del algoritmo de Canny, que son el cuello de botella causado por el proceso de histéresis y el uso de umbrales de histéresis fijos. Dada una imagen, esta se divide en un conjunto de sub-imágenes, y, para cada una de ellas, se calcula de forma no supervisada un par de umbrales de histéresis utilizando el método de Medina-Carnicer. El detector satisface el requisito de tiempo real, al ser 0.35 ms el tiempo promedio en detectar los bordes de una imagen 512x512.

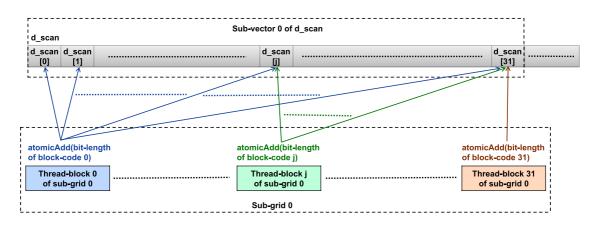

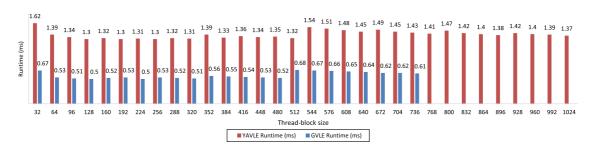

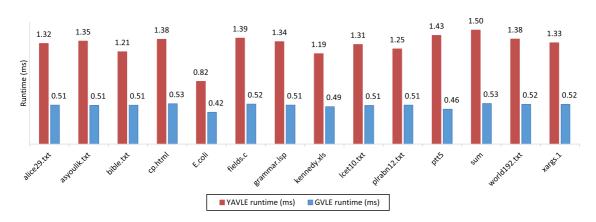

En tercer lugar, se ha realizado una implementación optimizada del método de compresión de datos VLE (Variable-Length Encoding), que es 2.6x más rápida en promedio que la mejor implementación anterior. Además, esta solución incluye un nuevo método scan inter-bloque, que se puede usar para acelerar la propia operación scan y otros algoritmos, como el de compactación. En el caso de la operación scan, se logra una aceleración de 1.62x si se usa el método propuesto en lugar del utilizado en la mejor implementación anterior de VLE.

Esta tesis doctoral concluye con un capítulo sobre futuros trabajos de investigación que se pueden plantear a partir de sus contribuciones.

A mis seres queridos, del cielo y de la tierra

# Agradecimientos

En primer lugar, a mis directores, Dr. Juan Gómez Luna y Dr. Rafael Medina Carnicer, por sus valiosas orientaciones en la dirección de esta tesis doctoral.

A mis hermanos, José María y Javier, de los que no me puedo sentir más orgulloso, por la fuerza y el entusiasmo que me han transmitido, y a mis sobrinos, Sara, María y José María, inmejorables reflejos de sus padres, por la alegría que me han regalado.

A mi compañera de viaje, María del Mar, por su apoyo sin límites. No tengo palabras para agradecer su comprensión, su generosidad y su optimismo.

Por último, a mis maravillosos padres, Antonio y Gema, por no sólo darme la vida, sino por iluminar constantemente su trayecto y ser mis mejores referentes.

# Índice

| . Introducción                                                                                      | 13                    |

|-----------------------------------------------------------------------------------------------------|-----------------------|

| 1.1. CUDA                                                                                           | 14                    |

| 1.2. Antecedentes                                                                                   | 16                    |

| 1.3. Objetivos                                                                                      | 17                    |

| 2. Contribuciones                                                                                   | 19                    |

| 2.1. Primera contribución: "CAVLCU: an efficient GPU-based implen<br>CAVLC"                         | nentation of<br>19    |

| 2.2. Segunda contribución: "GUD-Canny: a real-time GPU-based un<br>distributed Canny edge detector" | supervised and<br>57  |

| 2.3. Tercera contribución: "GVLE: a Highly Optimized GPU-Based Im<br>Variable-Length Encoding"      | plementation of<br>75 |

| 8. Conclusiones y futuros trabajos                                                                  | 105                   |

| 3.1. Conclusiones                                                                                   | 105                   |

| 3.2. Futuros trabajos                                                                               | 106                   |

| Referencias                                                                                         | 107                   |

|                                                                                                     |                       |

# 1. Introducción

Hoy en día, la computación de propósito general en unidades de procesamiento de gráficos, denominada abreviadamente *GPGPU* (General Purpose Computing on Graphics Processing Units), es una de las tendencias principales en la computación de alto rendimiento [1]. En los años 2000, la creciente demanda del mercado de videojuegos causó un incremento muy significativo de la capacidad de computación de las GPUs, en contraste con la más lenta evolución de las CPUs [2]. Este hecho ofreció la gran oportunidad de acelerar la resolución de problemas de propósito general mediante un procesamiento repartido entre CPU y GPU (en lugar de realizarlo exclusivamente la CPU) [2]. En 2007, para facilitar este sistema heterogéneo de computación, NVIDIA lanzó la arquitectura de cálculo paralelo CUDA (Compute Unified Device Architecture) [3], que, desde entonces, viene incorporada en sus tarjetas gráficas. CUDA proporciona un conjunto de herramientas de desarrollo y extensiones a lenguajes de programador [4, 5].

Desde hace una década y media, se están acelerando cientos de aplicaciones en GPU en los más diversos campos [6], como el aprendizaje automático [7, 8], el procesamiento de vídeo e imagen [9, 10] y la minería de datos [11, 12]. Sin embargo, aún existen algoritmos científicos poco explorados, como los métodos de compresión de datos CAVLC (Context-based Adaptive Variable Length Coding) [13, 14], CABAC (Context-based Adaptive Binary Arithmetic Coding) [15] y VLE (Variable-Length Encoding) [16, 17], y diferentes métodos de procesamiento de vídeo e imagen, como la detección de bordes de Canny no supervisada [18], el cálculo del descriptor de imágenes RCD (Region Covariance Descriptor) [19], la identificación de texturas a gran escala en tiempo real [20] y el algoritmo de eliminación de ruido de vídeo VBM3D (Video Block-Matching and 3-D Filtering) [21]. Por ello, la motivación de esta tesis ha sido investigar la posibilidad de acelerar significativamente en GPU un conjunto de algoritmos científicos pertenecientes a este grupo.

El resto de este capítulo introductorio se divide en las siguientes secciones. La sección 1.1 proporciona un breve resumen de CUDA para facilitar la comprensión de las optimizaciones desarrolladas en esta tesis, la sección 1.2 presenta sus antecedentes, y la 1.3, sus objetivos.

# 1.1. CUDA

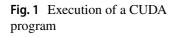

CUDA [3] es una plataforma de computación paralela de propósito general que aprovecha el motor de cálculo paralelo de sus GPUs para la resolución de problemas computacionalmente complejos de forma mucho más eficiente que usando sólo una CPU [4].

Los objetivos de diseño de CUDA fueron los siguientes [4]:

- Proporcionar un conjunto pequeño de extensiones a lenguajes de programación estándar, como C, C++, Fortran, Python y MATLAB, con objeto de facilitar enormemente el desarrollo de algoritmos paralelos [3]. De esta forma, se eliminó la necesidad de tener que usar lenguajes de programación específicos para gráficos (como OpenGL o Cg) para la resolución de problemas de propósito general, lo cual es mucho más complejo. En este trabajo, se ha utilizado CUDA C++ [4, 5].

- Soportar computación heterogénea, consistente en que las aplicaciones ejecuten sus partes secuenciales en la CPU y las paralelas en la GPU. La CPU y la GPU (denominadas *host* y *device*, respectivamente) se modelan como dispositivos separados, con sus propios espacios de memoria.

CUDA permite definir funciones, denominadas *kernels*, que son ejecutadas por muchos hilos en paralelo en la GPU [4]. Los hilos se organizan en *bloques*, que pueden tener entre una y tres dimensiones. Un kernel es ejecutado por un conjunto de bloques idénticos, denominado *grid*, cuyo número de dimensiones también puede ser hasta tres.

La arquitectura de una GPU de CUDA se compone de un conjunto de *multiprocesadores de streaming* [4]. Cuando un programa que está siendo ejecutado por la CPU llama a un kernel, los bloques del correspondiente grid se distribuyen a los multiprocesadores con capacidad de ejecución disponibles. Los hilos de cada bloque se ejecutan concurrentemente en un único multiprocesador, y, a su vez, cada multiprocesador puede ejecutar concurrentemente muchos bloques. Conforme va finalizando la ejecución de los bloques, otros nuevos se van lanzando en los multiprocesadores vacantes. Para que un kernel escale con el número de multiprocesadores de cualquier tarjeta gráfica, los bloques se deben poder ejecutar independientemente, es decir, en cualquier orden y en paralelo o en serie.

Un multiprocesador ejecuta los bloques en grupos de 32 hilos consecutivos, denominados *warps* [4]. Cada bloque, tras ser asignado a un multiprocesador, es dividido en warps, y cada warp es gestionado por un *planificador de warps*. Los hilos de un warp comienzan en la misma dirección de programa, pero cada uno tiene sus propios contador de programa y registro de estado, por lo que diferentes conjuntos de hilos de un mismo warp pueden seguir caminos de ejecución independientes. Aunque, a efectos de la corrección del código, no es necesario tener en cuenta esta característica de la arquitectura de CUDA, se pueden conseguir mejoras significativas en el rendimiento disminuyendo al máximo las divergencias de ejecución de los warps.

Los hilos de CUDA pueden acceder a los siguientes espacios de memoria [4] durante su ejecución:

- *Memoria privada* de cada hilo, constituida por *registros* y *memoria local*, cuyo tiempo de vida coincide con el del hilo.

- Memoria compartida, de baja latencia y visible a todos los hilos de un bloque, cuyo tiempo de vida es el del bloque.

- Un conjunto de memorias usadas para la compartición de datos entre todos los hilos de un grid, que son una memoria global de lectura/escritura y otras dos de lectura: la memoria de constantes, usada para almacenar valores no modificables, y la memoria de texturas, optimizada para accesos con localidad espacial 2D. Los contenidos de estas memorias son persistentes entre llamadas a kernels de una misma aplicación.

La memoria global es la más abundante de todas [5]. Por otro lado, las memorias global, local y de texturas tienen la latencia más alta, seguidas de la memoria de constantes, la memoria compartida y el espacio de registros [5].

Una técnica de optimización muy importante es el *acceso coalescente* a la memoria global [5]. Cuando un warp realiza una operación en memoria global, los accesos a memoria de sus hilos se unen en una o más transacciones de memoria, según el tamaño de las palabras accedidas y la distribución de las direcciones de memoria. Cuanto más

dispersos estén los accesos, más transacciones son necesarias y, por tanto, más se reduce el rendimiento.

# 1.2. Antecedentes

Aunque actualmente hay cientos de aplicaciones aceleradas en GPU en los más diversos campos [6], aún existen algoritmos científicos poco explorados, como los métodos de compresión de datos CAVLC [13, 14] y VLE [16, 17].

En el caso de CAVLC, la única implementación en GPU anterior a esta tesis es la propuesta por Su et al. [13, 14], desarrollada en CUDA. Satisface el requisito de tiempo real para el formato HDTV 720p, y su rendimiento es entre 6.29 y 11.17 veces mayor que el de los sistemas DSP y multinúcleo publicados hasta ese momento. Aunque se trata de una solución eficiente, existen diferentes factores que limitan su velocidad. El principal de ellos es que, al estar implementada con varios kernels, existe una penalización importante en la eficiencia causada por:

- Los accesos a memoria global de elevada latencia que se han de realizar para transmitir resultados intermedios entre kernels.

- Las costosas llamadas y finalizaciones de los distintos kernels.

En relación a las implementaciones de VLE en GPU, los antecedentes de este trabajo son el algoritmo PAVLE de Balevic [16] y la solución de Rahmani et al. [17]. La evaluación experimental mostró que la aceleración respecto a la implementación en CPU fue 35x, en el primer caso, y 22x, en el segundo. El principal factor que limita la velocidad de estas dos soluciones es el mismo que el de la implementación de CAVLC de Su et al. [13, 14].

Por último, indicar que, antes de esta tesis, se obtuvo el algoritmo CUVLE [22], una implementación eficiente en GPU de VLE. La evaluación experimental mostró que CUVLE es más de dos veces más rápido que PAVLE [16].

# 1.3. Objetivos

El objetivo general de esta tesis ha sido investigar las posibilidades de acelerar un conjunto de algoritmos científicos en entornos heterogéneos basados en GPU, con la finalidad de realizar contribuciones en cada uno de los siguientes objetivos específicos:

- Estudiar la posibilidad de optimizar el método de codificación entrópica CAVLC del estándar de compresión de vídeo H.264.

- Profundizar en la investigación sobre la optimización de VLE en arquitecturas paralelas de última generación.

- 3. Explorar la posibilidad de optimizar aplicaciones de vídeo e imagen en arquitecturas paralelas a determinar durante el transcurso de la investigación.

# 2. Contribuciones

# 2.1. Primera contribución: "CAVLCU: an efficient GPU-based implementation of CAVLC"

En este trabajo [23] se presenta CAVLCU, una implementación eficiente de CAVLC en GPU, que es útil en los siguientes escenarios:

- Se puede aprovechar como el componente de codificación entrópica en codificadores H.264 software, una alternativa adecuada a los codificadores H.264 hardware de las tarjetas gráficas [24] cuando estos últimos carecen de cierta funcionalidad necesaria, como encriptación de datos [25, 26, 27, 28] y ocultación de información [29, 30, 31, 32].

- Se puede utilizar en una amplia variedad de sistemas de compresión basados en GPU para codificar imágenes y vídeos en formatos diferentes a H.264, como imágenes médicas [33, 34, 35]. Esto no es posible con las implementaciones hardware de CAVLC, al no ser componentes separables de los codificadores H.264 hardware en los que están integradas.

CAVLCU se basa en cuatro ideas clave:

- Está compuesto de un solo kernel para evitar los accesos de elevada latencia a memoria global para transmitir resultados intermedios entre kernels, así como los costosos lanzamientos y terminaciones de estos últimos.

- Se aplica un mecanismo eficiente de sincronización entre bloques de hilos que procesan regiones adyacentes del fotograma (en las dimensiones horizontal y vertical) para compartir resultados en memoria global.

- Se explota completamente el ancho de banda de memoria global disponible mediante accesos vectorizados que almacenan directamente los coeficientes transformados cuantificados en registros.

- Se realiza la ordenación en zigzag de los bloques de coeficientes directamente en el espacio de registros con un alto grado de paralelismo a nivel de instrucción.

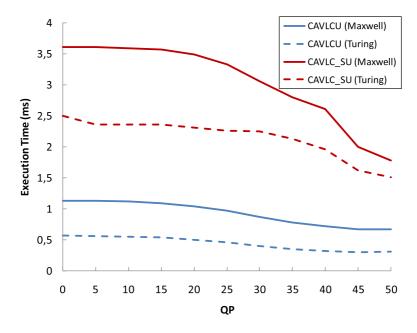

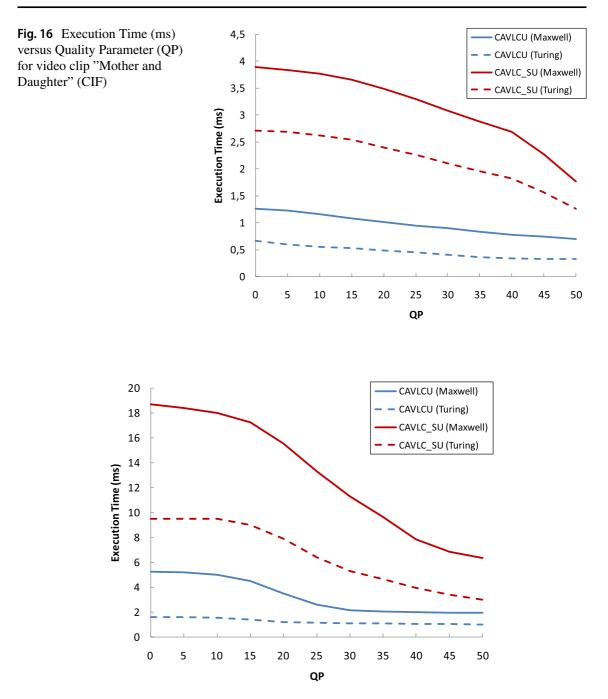

La evaluación experimental mostró que CAVLCU es entre 2.5x y 5.4x más rápido que la mejor implementación anterior en GPU de CAVLC [13].

Esta contribución se corresponde, como resultado, con los objetivos 1 y 3.

# CAVLCU: an efficient GPU-based implementation of CAVLC

Antonio Fuentes-Alventosa<sup>1</sup> · Juan Gómez-Luna<sup>2</sup> · José Maria González-Linares<sup>3</sup> · Nicolás Guil<sup>3</sup> · R. Medina-Carnicer<sup>1</sup>

Accepted: 27 October 2021 / Published online: 29 November 2021 © The Author(s) 2021

# Abstract

CAVLC (Context-Adaptive Variable Length Coding) is a high-performance entropy method for video and image compression. It is the most commonly used entropy method in the video standard H.264. In recent years, several hardware accelerators for CAVLC have been designed. In contrast, high-performance software implementations of CAVLC (e.g., GPU-based) are scarce. A high-performance GPU-based implementation of CAVLC is desirable in several scenarios. On the one hand, it can be exploited as the entropy component in GPU-based H.264 encoders, which are a very suitable solution when GPU built-in H.264 hardware encoders lack certain necessary functionality, such as data encryption and information hiding. On the other hand, a GPU-based implementation of CAVLC can be reused in a wide variety of GPU-based compression systems for encoding images and videos in formats other than H.264, such as medical images. This is not possible with hardware implementations of CAVLC, as they are non-separable components of hardware H.264 encoders. In this paper, we present CAVLCU, an efficient implementation of CAVLC on GPU, which is based on four key ideas. First, we use only one kernel to avoid the long latency global memory accesses required to transmit intermediate results among different kernels, and the costly launches and terminations of additional kernels. Second, we apply an efficient synchronization mechanism for thread-blocks (In this paper, to prevent confusion, a block of pixels of a frame will be referred to as simply block and a GPU thread block as thread-block.) that process adjacent frame regions (in horizontal and vertical dimensions) to share results in global memory space. Third, we exploit fully the available global memory bandwidth by using vectorized loads to move directly the quantized transform coefficients to registers. Fourth, we use register tiling to implement the zigzag sorting, thus obtaining high instruction-level parallelism. An exhaustive experimental evaluation showed that our approach is between 2.5× and 5.4× faster than the only state-of-the-art GPUbased implementation of CAVLC.

Keywords CAVLC  $\cdot$  GPU  $\cdot$  CUDA  $\cdot$  H.264  $\cdot$  Parallel implementations  $\cdot$  Data compression  $\cdot$  Variable-length encoding

Extended author information available on the last page of the article

#### 1 Introduction

In the current digital era, the massive use of multimedia data, such as images and videos, together with the necessity to overcome the restrictions of storage space and communication bandwidth, have given an essential role to data compression.

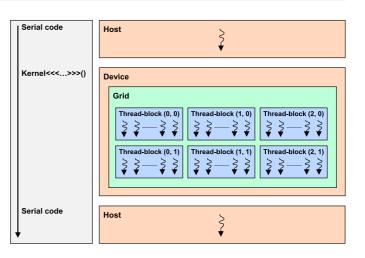

Generally speaking, data compression can be *lossless* or *lossy*, depending on whether the original content is preserved or not [33]. Lossless compression is used when it is necessary that the original and uncompressed data remain exactly the same, such as executable programs and textual documents. Lossy compression discards some information to increment the amount of data reduction. Image file formats like PNG use only lossless compression, while others like TIFF may use either lossless or lossy methods [2]. *Entropy coding* [33] is a type of lossless compression in which mostly used patterns are assigned with codes of shorter length, whereas rarely used patterns are assigned with codes of longer length.

*CAVLC* (Context-Adaptive Variable Length Coding) is a high-performance entropy technique for video and image compression [14, 32]. In this method, different sets of variable-length codes are chosen depending on already encoded syntax elements. It is the most commonly used entropy technique in the video standard H.264.

In the last two decades, many designs for CAVLC have been proposed. The majority of these solutions are based on hardware, such as FPGA [4, 6, 12, 28] and ASIC approaches [1, 3, 13, 21]. In contrast, parallel software implementations of CAVLC [5, 31, 38, 39, 43] are currently very scarce.

One of the most successful trends in high-performance computing is generalpurpose computation on graphics processing units (*GPGPU*), thanks to programming environments such as CUDA [26] and OpenCL [15]. Efficient implementations of CAVLC on GPU are currently very useful for the following reasons. First, they can be exploited as the entropy component in GPU-based H.264 encoders, which are a very suitable solution when it is necessary to implement functionality not provided by GPU built-in H.264 hardware encoders (e.g., NVENC in NVIDIA graphics cards [27]). In that case, many adaptations of CAVLC proposed in different fields, like data encryption [19, 40–42] and information hiding [16, 17, 45, 46], can be applied. Second, implementations of CAVLC on GPU can be reused and easily adapted in the development of a great variety of GPGPU compression systems for encoding both images and videos in formats other than H.264, like medical images [20, 30, 37]. This is not possible with hardware implementations of CAVLC, as they are non-separable components of hardware H.264 encoders.

In this paper, we present CAVLCU, an optimized implementation of CAVLC on GPU developed in CUDA. As our approach is built using only one CUDA kernel, it avoids the long latency global memory accesses required to transmit intermediate results among different kernels, and the costly launches and terminations of additional kernels. In our algorithm, thread-blocks that process adjacent frame regions (in horizontal and vertical dimensions) share results in global memory space using an efficient synchronization mechanism. Additionally, CAVLCU simplifies the zigzag sorting of the blocks, as each thread, after reading its block through a vectorized load, sorts it efficiently in the register space through few high throughput operations with high degree of instruction-level parallelism.

Therefore, our main contributions in this work are the following. First, a highly optimized GPU-based approach to CAVLC implemented in CUDA. Second, comparison of our implementation with the only existing state-of-the-art GPGPU implementation [38, 39]. An exhaustive experimental evaluation showed that our solution is between  $2.5 \times$  and  $5.4 \times$  faster than the state-of-the-art implementation [38, 39].

The rest of the paper is organized as follows. Sections 2 and 3 give background for CAVLC and the state-of-the-art GPU-based implementation of CAVLC [38, 39], respectively. Section 4 presents CAVLCU. Section 5 shows the experimental evaluation of our algorithm and a comparison to the state-of-the-art solution [38, 39]. Section 6 presents applications of CAVLC. Finally, the main conclusions are stated in Sect. 7.

#### 2 Context-adaptive variable length coding (CAVLC)

*CAVLC* (Context-Adaptive Variable Length Coding) [14, 32] is a high efficient entropy method for encoding the quantized transform coefficients in video and image compression. In this technique, different sets of variable-length codes are chosen depending on already encoded syntax elements. Since the variable-length codes are designed to match the corresponding conditioned statistics, the entropy coding performance is improved by 5-10% in comparison to prior standards designs (like MPEG, H.261/3) using a single variable-length code.

CAVLC is one of the two entropy methods in H.264 [14], the most widely used video coding standard [29]. The alternative is *CABAC* (Context-Adaptive Binary Arithmetic Coding) [32], a method of arithmetic coding in which the probability models are updated based on previous coding statistics. Compared to CABAC, CAVLC has lower compression efficiency, but higher coding speed and lower complexity. Thus, it is widely used in low-delay, 'conversational' applications such as video conferencing, with relatively low computational requirements. Moreover, CAVLC is supported in all H.264 profiles, unlike CABAC which is not supported in baseline and extended profiles.

Next, Subsection 2.1 gives a detailed description of CAVLC algorithm, and Subsection 2.2 presents an example to clarify its operation.

#### 2.1 CAVLC algorithm

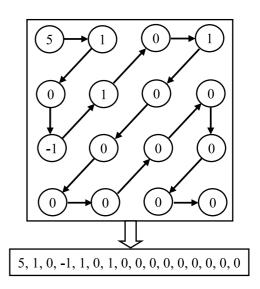

CAVLC operates on blocks of  $4\times4$  and  $2\times2$  coefficients. It follows the steps presented in Algorithm 1 for encoding a block [32]. First, as shown in Fig. 1 for a  $4\times4$  block, the coefficients are scanned in zigzag order. The resulting array will be referred to as *zigzag array* in the rest of the paper. Then, CAVLC constructs the output bitstream by concatenating a series of binary variable length codes (*VLCs*) assigned to the following data elements (*symbols*) of the zigzag array: *CoeffToken*,

Fig. 1 Example of zigzag scan for a  $4 \times 4$  block

*trailing ones, levels, TotalZeros* and *runs*. In the next subsections, we define the referenced symbols and describe how they are encoded.

| Algorithm 1: CAVLC block encoding. The opera-<br>tor & represents binary concatenation |

|----------------------------------------------------------------------------------------|

| zigzag array $\leftarrow$ scan the coefficients of the block<br>in zigzag order        |

| encoding $\leftarrow$ VLC of symbol CoeffToken of zigzag array &                       |

| Bit signs of trailing ones of zigzag array<br>&                                        |

| VLCs of levels of zigzag array<br>&                                                    |

| VLC of symbol TotalZeros of zigzag array<br>&                                          |

| VLCs of runs of zigzag array                                                           |

#### 2.1.1 CoeffToken

The magnitude of nonzero coefficients tends to be larger at the start of the zigzag array, near the first coefficient, and smaller towards the higher frequencies. In addition, the absolute value of the last nonzero coefficients often equals to 1. The last up to three -1 or +1 coefficients are referred to as *trailing ones* (*T1s*), while the remaining nonzero coefficients as *levels*. The symbol *CoeffToken* (coefficient token) represents both the total number of nonzero coefficients (*TotalCoeff*) and the number of trailing ones (*NumT1s*).

The VLC assigned to CoeffToken is obtained from a lookup table that, in the case of a  $4 \times 4$  block, is chosen from three VLC tables and one 6-bit fixed length code table, whose contents are specified in Table 9-5 of the H.264 standard [14]. An extract of this latter is shown in Table 1. As it can be seen, the choice of the

| NumT1s | TotalCoeff | $0 \le nC < 2$      | $2 \le nC < 4$    | $4 \le nC < 8$ | $8 \le nC$ |

|--------|------------|---------------------|-------------------|----------------|------------|

| 0      | 0          | 1                   | 11                | 1111           | 0000 11    |

| 0      | 1          | 0001 01             | 0010 11           | 0011 11        | 0000 00    |

|        | •••••      |                     |                   |                |            |

|        |            |                     |                   |                |            |

| 2      | 5          | 0000 0010 1         | 0000 101          | 0100 1         | 0100 10    |

| 3      | 5          | 0000 100            | 0011 0            | 1010           | 0100 11    |

|        |            |                     |                   |                |            |

|        |            |                     |                   |                |            |

| 2      | 16         | 0000 0000 0000 0101 | 0000 0000 0001 01 | 0000 0000 11   | 1111 10    |

| 3      | 16         | 0000 0000 0000 1000 | 0000 0000 0001 00 | 0000 0000 10   | 1111 11    |

Table 1

Extract of the table 9-5 of the H.264 standard

lookup table is done in function of a parameter nC, which is calculated from the number of coefficients in the blocks to the left and above of the current block (parameters nA and nB, respectively). This implies that the lookup table selection is context adaptive. Figure 2 illustrates the relationship between a block and its neighbours. The parameter nC is calculated as shown in Table 2, where >> indicates binary right shift. The availability of each neighbouring block is determined by its existence and its membership in the same slice of the current block.

| <b>Fig. 2</b> Relationship between current block and its top and left  |                                   |            | Upper block      |

|------------------------------------------------------------------------|-----------------------------------|------------|------------------|

| neighbours                                                             |                                   |            | nB               |

|                                                                        |                                   | nA         | nC               |

|                                                                        |                                   | Left block | Current<br>block |

| Table 2         Calculation of           parameter nC. The operator >> | Condition                         | nC         |                  |

| represents binary right shift                                          | Left and top blocks are available | (nA        | + nB + 1) >>1    |

|                                                                        | Only the left block is available  | nA         |                  |

|                                                                        | Only the top block is available   | nB         |                  |

|                                                                        | Neither neighbouring block is ava | ilable 0   |                  |

#### 2.1.2 Trailing ones

The T1s are encoded in reverse order with their sign bits ('0' for positive and '1' for negative).

#### 2.1.3 Levels

The levels are encoded in reverse order with VLCs composed of a prefix and a possible suffix. The prefix is made up of a string of zero or more bits '0' followed by a stop bit '1'. The length of the suffix (*SuffixLength*) is between 0 and 6 in normal cases. If SuffixLength > 0, the last bit of the suffix stores the sign of the level.

Table 3 shows an extract of the seven VLC tables used for levels encoding in the H.264 baseline profile [11], each one corresponding to a different value of

| Lev-VLCT[0]            |                           |           |        |  |  |  |  |

|------------------------|---------------------------|-----------|--------|--|--|--|--|

| Level                  | VLC                       | Length    |        |  |  |  |  |

| +1                     | 1                         | 1         |        |  |  |  |  |

| -1                     | 01                        | 2         |        |  |  |  |  |

| +2                     | 001                       | 3         |        |  |  |  |  |

| -2                     | 0001                      | 4         |        |  |  |  |  |

|                        |                           |           |        |  |  |  |  |

| +7                     | 000000000001              | 13        |        |  |  |  |  |

| -7                     | 0000000000001             | 14        |        |  |  |  |  |

| $\pm 8$ to $\pm 15$    | 000000000000001xxxx       | 19        |        |  |  |  |  |

| $\geq \pm 16$          | 000000000000001xxxxxxxxxx | 28        |        |  |  |  |  |

| Lev-VLCT[1]            |                           |           |        |  |  |  |  |

| Level                  | VLC                       |           | Length |  |  |  |  |

| ± 1                    | 1x                        |           | 2      |  |  |  |  |

| ±2                     | 01x                       |           | 3      |  |  |  |  |

|                        |                           |           |        |  |  |  |  |

| ± 5                    | 00001x                    |           | 6      |  |  |  |  |

| ± 15                   | 00000000000001x           |           | 16     |  |  |  |  |

| $\geq \pm 16$          | 000000000000001xxx        | XXXXXXXXX | 28     |  |  |  |  |

|                        |                           |           |        |  |  |  |  |

| Lev-VLCT[6]            |                           |           |        |  |  |  |  |

| Level                  | VLC                       |           | Length |  |  |  |  |

| $\pm 1$ to $\pm 32$    | 1xxxxxx                   |           | 7      |  |  |  |  |

| $\pm 33$ to $\pm 64$   | 01xxxxxx                  |           | 8      |  |  |  |  |

|                        |                           |           |        |  |  |  |  |

| $\pm 449$ to $\pm 480$ | 00000000000001xxxx        | xxx       | 21     |  |  |  |  |

| $\geq \pm 481$         | 000000000000001xxx        | xxxxxxxxx | 28     |  |  |  |  |

Table 3 VLC Tables of levels

SuffixLength. Table Lev-VLCT[0] is selected for SuffixLength = 0, Table Lev-VLCT[1] for SuffixLength = 1, and so on. Lev-VLCT[0] has its own structure while the remaining VLC tables share a common structure. In all cases, when the magnitude of the level is too large, its value is stored entirely in the suffix, whose length is set to 12. As the last bit represents the sign, the maximum magnitude that CAVLC can encode is  $2^{11} = 2048$  in the baseline profile [11].

Algorithm 2 [14, 32] shows how the levels are encoded. The selection of each VLC table is context adaptive, as it depends on the magnitude of the previous coded level.

```

Algorithm 2: CAVLC levels encoding

if TotalCoeff > 10 and NumT1s < 3 then</pre>

SuffixLength \leftarrow 1

else

SuffixLength \leftarrow 0

end if

for each level in reverse order do

effective_level \leftarrow level

if level is the first to encode and NumT1s < 3 then</pre>

subtract 1 to magnitude of effective_level

end if

encode effective_level using Lev-VLCT[SuffixLength]

if SuffixLength = 0 then

SuffixLength \leftarrow 1

end if

if SuffixLength < 6 then</pre>

T \leftarrow 3 \times 2^{SuffixLength - 1}

if magnitude(level) > T then

SuffixLength ← SuffixLength + 1

end if

end if

end for

```

#### 2.1.4 TotalZeros

The symbol *TotalZeros* is the sum of all zeros preceding the last nonzero coefficient in the zigzag array. The VLC assigned to TotalZeros is obtained from a lookup table that, in the case of a  $4 \times 4$  block, is selected from 15 VLC tables, whose contents are specified in Tables 9-7 and 9-8 of the H.264 standard [14]. An extract of these tables is shown in Tables 4 and 5. As it can be seen, the choice of the lookup table is done in function of the symbol TotalCoeff. If TotalCoeff is 0 or 16, TotalZeros is not encoded because it is known that all coefficients are zero or nonzero, respectively.

| TotalZeros | TotalCoeff  |         |        |        |      |         |         |  |  |  |

|------------|-------------|---------|--------|--------|------|---------|---------|--|--|--|

|            | 1           | 2       | 3      | 4      | 5    | 6       | 7       |  |  |  |

| 0          | 1           | 111     | 0101   | 0001 1 | 0101 | 0000 01 | 0000 01 |  |  |  |

| 1          | 011         | 110     | 111    | 111    | 0100 | 0000 1  | 0000 1  |  |  |  |

| 2          | 010         | 101     | 110    | 0101   | 0011 | 111     | 101     |  |  |  |

|            |             |         |        |        |      |         |         |  |  |  |

|            |             |         | •••••• |        |      |         |         |  |  |  |

| 14         | 0000 0001 0 | 0000 00 | _      | _      | _    | _       | _       |  |  |  |

| 15         | 0000 0000 1 | _       | _      | _      | _    | _       | _       |  |  |  |

Table 4

Extract of the table 9-7 of the H.264 standard

| <b>Table 5</b> Extract of the table 9-8of the H.264 standard | TotalZeros | TotalCoe | eff     |        |      |      |     |    |    |

|--------------------------------------------------------------|------------|----------|---------|--------|------|------|-----|----|----|

|                                                              |            | 8        | 9       | 10     | 11   | 12   | 13  | 14 | 15 |

|                                                              | 0          | 0000 01  | 0000 01 | 0000 1 | 0000 | 0000 | 000 | 00 | 0  |

|                                                              | 1          | 0001     | 0000 00 | 00000  | 0001 | 0001 | 001 | 01 | 1  |

|                                                              | 2          | 0000 1   | 0001    | 001    | 001  | 01   | 1   | 1  | _  |

|                                                              |            |          |         |        |      |      |     |    |    |

|                                                              | 7          | 001      | 0000 1  | _      | _    | _    | _   | _  | _  |

|                                                              | 8          | 0000 00  | -       | _      | _    | _    | _   | _  | _  |

#### 2.1.5 Runs

The parameter run of a nonzero coefficient is defined as the sum of all consecutive zeros that precede it. The runs are encoded in reverse order using one of the 7 VLC tables specified in Table 9-10 of the H.264 standard [14], whose content is presented in Table 6. The selection of each VLC is done in function of the symbol run and a second parameter, called ZerosLeft, which is the number of zeros that remain to be encoded. ZerosLeft is initialized to TotalZeros and decreases as more runs are encoded. The runs encoding is finished in the following two cases: (1) All zeros have already been encoded. (2) The current nonzero coefficient is the last in the reverse order, which implies that the maximum value to be encoded is 14.

| Table 6Tables for runsencoding | Run | Zero | sLeft |    |     |     |     |            |

|--------------------------------|-----|------|-------|----|-----|-----|-----|------------|

| encounts                       |     | 1    | 2     | 3  | 4   | 5   | 6   | >6         |

|                                | 0   | 1    | 1     | 11 | 11  | 11  | 11  | 111        |

|                                | 1   | 0    | 01    | 10 | 10  | 10  | 000 | 110        |

|                                | 2   | -    | 00    | 01 | 01  | 011 | 001 | 101        |

|                                | 3   | _    | _     | 00 | 001 | 010 | 011 | 100        |

|                                | 4   | _    | _     | _  | 000 | 001 | 010 | 011        |

|                                | 5   | _    | _     | _  | _   | 000 | 101 | 010        |

|                                | 6   | _    | _     | _  | _   | _   | 100 | 001        |

|                                | 7   | -    | -     | _  | -   | -   | -   | 0001       |

|                                | 8   |      | _     | _  | _   | _   | _   | 00001      |

|                                | 9   | _    | -     | _  | _   | _   | _   | 000001     |

|                                | 10  | _    | _     | _  | _   | _   | _   | 0000001    |

|                                | 11  | _    | _     | _  | _   | -   | _   | 00000001   |

|                                | 12  | _    | _     | _  | _   | _   | _   | 00000001   |

|                                | 13  | _    | _     | _  | _   | _   | _   | 000000001  |

|                                | 14  | _    | _     | _  | _   | _   | _   | 0000000001 |

#### 2.2 CAVLC example

In this subsection, we present an example of CAVLC encoding, corresponding to the  $4\times4$  block of Fig. 1. As shown, the zigzag array is  $\{5, 1, 0, -1, 1, 0, 1, 0, 0, 0, 0, 0, 0, 0, 0, 0\}$ .

We assume that the two neighbouring blocks are available, and that the values of the parameters nA and nB are 4 and 6, respectively. Hence, nC = (4 + 6 + 1) >> 1 = 5. As TotalCoeff = 5 and NumT1s = 3, the VLC assigned to CoeffToken is 1010 (see Table 1). Note that the last four nonzero coefficient have magnitude 1, but only the last three ones are taken into account.

The values of the T1s in reverse order are +1, +1, and -1. Therefore, the VLC assigned is 001.

The steps for levels encoding (see Algorithm 2 and Table 3) are the next:

- 1. TotalCoeff = 5 and NumT1s = 3, hence the condition TotalCoeff > 10 and NumT1s < 3 is not fulfilled and SuffixLength is initialized to 0.

- 2. The first level in the reverse order is +1. As the condition NumT1s < 3 is not satisfied, the absolute value of the level is not decremented.

- 3. SuffixLength is 0; hence, on the one hand, Lev-VLCT[0] is selected and the VLC assigned to level +1 is 1. On the other hand, SuffixLength is assigned the value 1.

- 4. As SuffixLength is less than 6, on the one hand, the threshold T is calculated: T  $= 3 \times 2^{SuffixLength-1} = 3 \times 2^{1-1} = 3$ . On the other hand, since magnitude(level) = 1 and T = 3, the condition magnitude(level) > T is not fulfilled and SuffixLength is not incremented.

5. The last level to encode is +5. As SuffixLength is 1, Lev-VLCT[1] is selected and the VLC assigned to level is 000010.

TotalZeros is 2 and TotalCoeff is 5. Therefore, the value assigned to TotalZeros is 0011 (see Table 4).

The runs of coefficients 5, 1, -1, 1 and 1 are 0, 0, 1, 0 and 1, respectively. Their encoding is done as follows (see Table 6):

- 1. Initially, the value of ZerosLeft equals to TotalZeros, i.e., 2.

- 2. The first run in the reverse order is 1 and ZerosLeft is 2; therefore, the VLC assigned is 01 and the value of ZerosLeft changes to 1.

- 3. The second run is 0 and ZerosLeft is 1; hence, the VLC assigned is 1 and the value of ZerosLeft does not change.

- 4. The third run is 1 and ZerosLeft is 1, therefore the VLC assigned is 0 and the value of ZerosLeft changes to 0.

- 5. As all zeros have been reached, the runs encoding is finished.

Finally, taking into account the different encodings seen in this subsection, the resulting bitstream of our example is the following: 1010-001-1-000010-0011-01-1-0

# 3 Solution of Su et al.

The only state-of-the-art GPU-based implementation of CAVLC is the solution presented by Su et al. [38, 39], which was developed in CUDA. It satisfies the real-time processing for HDTV 720p and its throughput is 11.17 to 6.29 times higher than that of the published software encoders on DSP and multi-core platforms.

By profiling the instructions of CAVLC, Su et al. found the main factors that limit the potential of parallelism [38, 39], which are the context-based data dependence, the memory accessing dependence and the control dependence. The context-based data dependence is due to the self-adaptive feature of CAVLC. Since the value of the parameter nC depends on nA and nB, it is not possible to calculate the parameter nC of a block until the symbols TotalCoeff of the neighbouring left and top blocks have been calculated. The memory accessing dependence is caused by the inherently serial nature of variable length encoding. To determine the position of each VLC in the output bitstream it is necessary to know the lengths of the VLCs that precede it. Control dependence is caused by the existence of different processing paths in two layers: the frame layer and the block layer. In the first layer, the branches are due to the different frame types and the different components of a frame (luma DC, luma AC, chroma DC and chroma AC). In the second layer, the different processing paths are caused by the irregular characteristic of symbol data, such as whether sign trail is 1 or -1 and whether levels are zero or not.

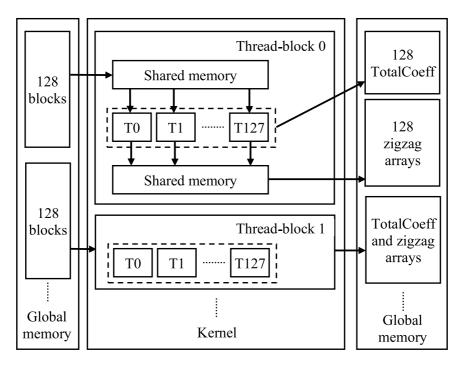

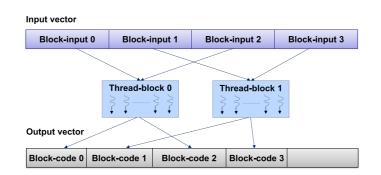

Fig. 3 Calculation of TotalCoeff and zigzag arrays in the solution of Su et al

Fig. 4 Calculation of nC and other symbols in the solution of Su et al

In order to eliminate or weaken the dependencies described above, Su et al. divided the execution of CAVLC into four paths according to the four components of a frame, and the CAVLC pipeline of each path was divided into three stages: two scans, coding and lag packing.

#### 3.1 Two scans

Two scans are employed to calculate the CAVLC symbols: a forward scan and a backward scan.

The forward scan aims at the quantized coefficients and the results include the symbols TotalCoeff and the zigzag arrays, as it is shown in Fig. 3. In this stage, each thread is assigned to deal with a block. In order to satisfy the requirement of coalesced access to global memory [22, 25], the shared memory is used as a buffer.

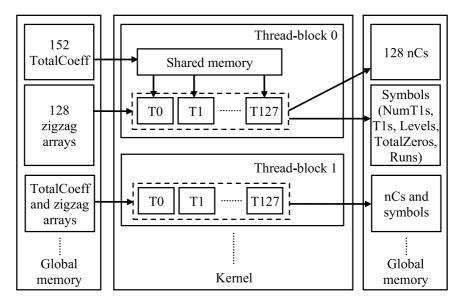

The backward scan is executed on the zigzag arrays generated in the first scanning and the results consist of the values of nC and the remaining CAVLC symbols (NumT1s, T1s, levels, TotalZeros and runs). In order to make better use of the local data, a frame is divided into several regions of  $4\times 2$  macroblocks. One thread-block calculates the values of nC of blocks in the same region, as it is shown in Fig. 4. The program first loads all data needed to the shared memory, then each thread visits nA and nB, where one symbol TotalCoeff can be used as either nA or nB.

#### 3.2 Coding

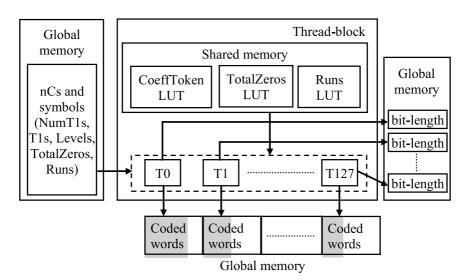

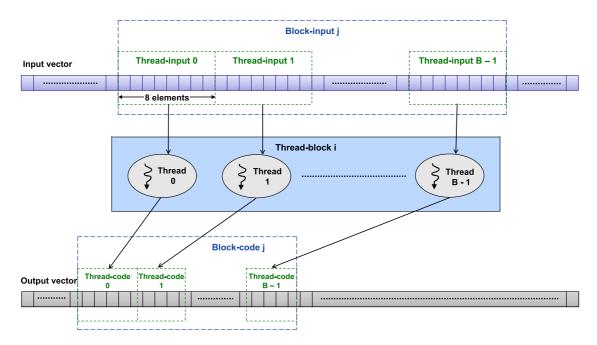

For the sake of minimizing the performance loss of the target parallel CAVLC encoder due to control dependence, Su et al. proposed a component-based coding mechanism. In this method, the program codes the symbols frame by frame in order of luma DC, luma AC, chroma DC, chroma AC instead of processing the four components macroblock by macroblock. The coding method is very similar for the different types of blocks; the main difference is the use of specific lookup tables for each component. In addition, the lookup tables are firstly loaded to the shared memory to speed up the lookup operation. The configuration is similar to that of calculating the value of nC and the results are the encodings (bitstreams and bit-lengths) of each block. A memory unit of 26 short words is used to store the bitstream of a block. Figure 5 shows the organization of a thread-block for encoding the symbols.

Fig. 5 Writing of encodings and bit-lengths in the solution of Su et al

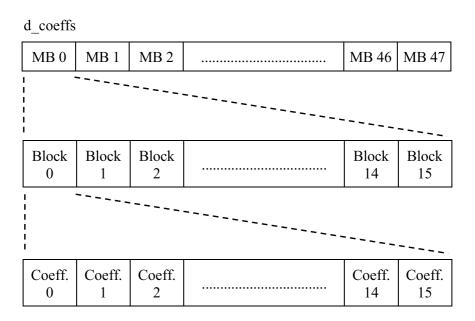

**Fig. 6** Layout of CAVLCU input vector of coefficients ( $d\_coeffs$ ) for SQCIF format (128×96). The array is divided in as many subvectors as MBs in the frame (48 in the case of SQCIF). Each MB subvector is divided into 16 subvectors, each one corresponding to a different block of the MB

In the vector of coded words, the grey areas represent the bitstreams of the encodings, while the white regions are the unused spaces.

# 3.3 Lag packing

Once all the blocks are encoded, parallel writing is executed. According to the lengths of the bitstreams, the output positions are obtained and a parallel packing is performed. Thus, it can not only eliminate the constraint of accessing dependence, but it also improves the performance of writing.

# 4 Efficient GPU-based implementation of CAVLC (CAVLCU)

In this section, we present *CAVLCU*, our parallel implementation of CAVLC on CUDA. It is also compared with Su et al. proposal so that the achieved performance improvement can be clearly established. Our solution is built using only one CUDA kernel that has been specifically designed for encoding the luma AC blocks of a frame. The method for the remaining types of blocks (luma DC, chroma DC and chroma AC) is essentially the same, with very few variations.

The inputs of CAVLCU are the following:

• The coefficients of the frame. They are provided in a vector of 16-bit integers (*d\_coeffs*), whose layout is shown in Fig. 6 for SQCIF format (128×96). As it can be seen, the array is divided in as many subvectors as macroblocks (*MBs*) in the frame (48 in the case of SQCIF format); the i-th subvector stores the coefficients of the i-th MB of the frame in the raster scan order (i.e., from left to right and

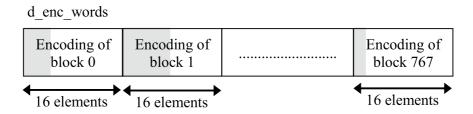

**Fig. 7** Layout of CAVLCU output vector of CAVLC encodings (d\_enc\_words) for SQCIF format (128× 96). The array is divided in as many subvectors of size 16 as blocks in the frame (768 in the case of SQCIF). The i-th subvector is used for storing the encoding of the i-th block of the frame. The grey areas correspond to the CAVLC encodings, whose lengths are variable

| Regi  | on 0  |       |       | Regi  | on 1  |       |       | Regi  | on 2   |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|-------|

| MB 0  | MB 1  | MB 2  | MB 3  | MB4   | MB 5  | MB 6  | MB 7  | MB 8  | MB 9   | MB 10 |

|       | Regi  | on 3  |       |       | Regi  | on 4  |       |       | Regi   | on 5  |

| MB 11 | MB12  | MB 13 | MB 14 | MB 15 | MB 16 | MB 17 | MB 18 | MB 19 | MB 20  | MB 21 |

|       |       | Regi  | on 6  |       |       | Regi  | on 7  |       |        |       |

| MB 22 | MB 23 | MB 24 | MB 25 | MB 26 | MB 27 | MB 28 | MB 29 | MB 30 | MB 31  | MB 32 |

| Regi  | on 8  |       | Regi  | on 9  |       |       | Regio | n 10  |        |       |

| MB 33 | MB 34 | MB 35 | MB 36 | MB 37 | MB 38 | MB 39 | MB 40 | MB 41 | MB 42  | MB 43 |

| Regi  | on 11 |       |       | Regio | on 12 |       |       | Reg   | ion 13 |       |

| MB 44 | MB 45 | MB 46 | MB 47 | MB 48 | MB 49 | MB 50 | MB 51 | MB 52 | MB 53  | MB 54 |

|       | Regi  | on 14 |       |       | Regio | on 15 |       |       | Regi   | on 16 |

| MB 55 | MB 56 | MB 57 | MB 58 | MB 59 | MB 60 | MB 61 | MB 62 | MB 63 | MB 64  | MB 65 |

|       |       | Regi  | on 17 |       |       | Regio | n 18  |       |        |       |

| MB 66 | MB 67 | MB 68 | MB 69 | MB 70 | MB 71 | MB 72 | MB 73 | MB 74 | MB 75  | MB 76 |

| Regi  | on 19 |       | Regi  | on 20 |       |       | Regio | n 21  |        |       |

| MB 77 | MB 78 | MB 79 | MB 80 | MB 81 | MB 82 | MB 83 | MB 84 | MB 85 | MB 86  | MB 87 |

| Regio | on 22 |       |       | Regio | on 23 |       |       | Regio | on 24  |       |

| MB 88 | MB 89 | MB 90 | MB 91 | MB 92 | MB 93 | MB 94 | MB 95 | MB 96 | MB 97  | MB 98 |

Fig. 8 Partition of a QCIF frame (176×144) in regions of size 4

from top to bottom). At the same time, each MB subvector is divided into 16 subvectors, each one corresponding to a different block of the MB; the i-th subvector stores the 16 coefficients of the i-th  $4\times4$  block of the MB. Both blocks and coefficients are provided in the raster scan order as well.

- The prediction modes of the MBs. They are supplied in a vector of 8-bit integers (*d\_MB\_pred\_modes*), where the i-th element is assigned to the i-th MB of the frame.

- The slice IDs of the MBs. They are provided in a vector of 16-bit integers (*d\_MB\_slices*), where the i-th element is assigned to the i-th MB of the frame.

Similarly, the outputs of CAVLCU are the following:

| 0 |  |  |  |

|---|--|--|--|

| v |  |  |  |

757

|           | MI        | 3 0       |           |           | MI        | 31        |           |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Blk 0     | Blk 1     | Blk 2     | Blk 3     | Blk 0     | Blk 1     | Blk 2     | Blk 3     |

| Th(0,0,0) | Th(1,0,0) | Th(2,0,0) | Th(3,0,0) | Th(0,0,1) | Th(1,0,1) | Th(2,0,1) | Th(3,0,1) |

| Blk 4     | Blk 5     | Blk 6     | Blk 7     | Blk 4     | Blk 5     | Blk 6     | Blk 7     |

| Th(0,1,0) | Th(1,1,0) | Th(2,1,0) | Th(3,1,0) | Th(0,1,1) | Th(1,1,1) | Th(2,1,1) | Th(3,1,1) |

| Blk 8     | Blk 9     | Blk 10    | Blk 11    | Blk 8     | Blk 9     | Blk 10    | Blk 11    |

| Th(0,2,0) | Th(1,2,0) | Th(2,2,0) | Th(3,2,0) | Th(0,2,1) | Th(1,2,1) | Th(2,2,1) | Th(3,2,1) |

| Blk 12    | Blk 13    | Blk 14    | Blk 15    | Blk 12    | Blk 13    | Blk 14    | Blk 15    |

| Th(0,3,0) | Th(1,3,0) | Th(2,3,0) | Th(3,3,0) | Th(0,3,1) | Th(1,3,1) | Th(2,3,1) | Th(3,3,1) |

# First half of region

# Second half of region

|           | MI                                              | 32        |           |           | MI        | 33        |           |

|-----------|-------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| Blk 0     | Blk 1                                           | Blk 2     | Blk 3     | Blk 0     | Blk 1     | Blk 2     | Blk 3     |

| Th(0,0,2) | Th(1,0,2)                                       | Th(2,0,2) | Th(3,0,2) | Th(0,0,3) | Th(1,0,3) | Th(2,0,3) | Th(3,0,3) |

| Blk 4     | Blk 5                                           | Blk 6     | Blk 7     | Blk 4     | Blk 5     | Blk 6     | Blk 7     |

| Th(0,1,2) | Th(1,1,2)                                       | Th(2,1,2) | Th(3,1,2) | Th(0,1,3) | Th(1,1,3) | Th(2,1,3) | Th(3,1,3) |

| Blk 8     | Blk 9                                           | Blk 10    | Blk 11    | Blk 8     | Blk 9     | Blk 10    | Blk 11    |

| Th(0,2,2) | Th(1,2,2)                                       | Th(2,2,2) | Th(3,2,2) | Th(0,2,3) | Th(1,2,3) | Th(2,2,3) | Th(3,2,3) |

| Blk 12    | Blk 13                                          | Blk 14    | Blk 15    | Blk 12    | Blk 13    | Blk 14    | Blk 15    |

| Th(0,3,2) | Th(1,3,2)                                       | Th(2,3,2) | Th(3,3,2) | Th(0,3,3) | Th(1,3,3) | Th(2,3,3) | Th(3,3,3) |

|           |                                                 |           |           |           |           |           |           |

| Ha        | Half-warp 0 Half-warp 1 Half-warp 2 Half-warp 3 |           |           |           |           |           |           |

**Fig. 9** Mapping of region data to elements of a thread-block in the case of region 7 of Fig. 8. The first MB of the region is assigned to the first half-warp of the thread-block, the second MB to the second half-warp, and so on. For each MB, the first block is assigned to the first thread of the corresponding half-warp, the second block to the second thread, and so on

- The encodings of the blocks. They are written in a vector of 32-bit integers, *d\_enc\_words*, where the i-th subvector of size 16 (*BLK\_ENC\_SIZE*) is used for storing the encoding of the i-th block of the frame, as Fig. 7 illustrates for SQCIF format.

- The binary lengths of the encodings. They are stored in a vector of 16-bit integers, *d\_enc\_lens*, where the i-th element is assigned to the i-th block of the frame.

As illustrated for a QCIF frame (176×144) in Fig. 8, CAVLCU divides a frame into equally-sized groups of consecutive MBs in the raster scan order, which will be referred to as *regions*. The execution configuration of the kernel uses a one-dimensional grid with as many thread-blocks as regions in the frame (*NUM\_REG*); the i-th thread-block of the grid processes the i-th region of the frame. The dimensions of the thread-blocks are  $4\times4\times$ REG\_SIZE, where *REG\_SIZE* is the number of MBs of each region. As it is shown in Fig. 9 for the region 7 of Fig. 8, the i-th MB of the

region is assigned to the i-th half-warp of the thread-block, and the i-th block of a MB is encoded by the i-th thread of the corresponding half-warp.

Algorithm 3 shows the pseudocode of CAVLCU kernel. The parameters *NUM\_MB*, *NUM\_BLK* and *NUM\_COEFF* represent, respectively, the number of MBs, 4×4 blocks and coefficients of the frame; on the other hand, *NUM\_WORD\_ENC* is the number of 32-bit words used for storing the CAVLC encodings of the frame, whose value is the product of *NUM\_BLK* by *BLK\_ENC\_SIZE*. Each thread performs the next steps. First, it calculates the indexes of the block to be encoded and the MB to which the block belongs. Second, it reads the coefficients of the block, and the prediction mode and slice ID of the MB. Third, it sorts the block in zigzag order to get the zigzag array. Fourth, it calculates a set of symbols from the zigzag array. Fifth, it calculates the block.

## Algorithm 3: CAVLCU algorithm

```

kernel CAVLCU(// outputs

d_enc_words[NUM_WORD_ENC],

d_enc_lens[NUM_BLK],

// inputs

d_coeffs[NUM_COEFF],

d_MB_pred_modes[NUM_MB],

d MB slices[NUM MB]

)

// Calculate the block and MB indexes

MB_idx \leftarrow blk_idx / 16

// Read the coefficients of the block

// Read the prediction mode and the slice ID of the MB

MB pred mode \leftarrow d MB pred modes[MB idx]

MB_slice \leftarrow d_MB_slices[MB_idx]

// Sort the block in zigzag order

short zz_array[16]

sort_in_zigzag_order(zz_array, block_vec)

// Calculate a set of symbols from the zigzag array

calculate_symbols(// outputs

TotalCoeff, NumT1s, T1s,

ZigzagLevelsMask, ZigzagArrayMask,

// inputs

zz_array, MB_pred_mode

)

encode_block(// outputs

d_enc_words, d_enc_lens,

// inputs

blk_idx,

TotalCoeff, NumT1s, T1s,

ZigzagLevelsMask, ZigzagArrayMask,

nC

end kernel

```

## 4.1 Calculation of block and MB indexes

As the i-th block of the frame is processed by the i-th thread of the grid, the index of the block equals to the thread ID in the grid, whose value is the following:

$blockIdx.x \times (blockDim.x \times blockDim.y \times blockDim.z)+$

+threadIdx.z  $\times$  blockDim.x  $\times$  blockDim.y+

$+threadIdx.y \times blockDim.x + threadIdx.x$

Since blockDim.x = blockDim.y = 4 and blockDim.z =  $REG_SIZE$ , the index of the block is calculated using the following expression:

$16 \times REG\_SIZE \times blockIdx.x + 16 \times threadIdx.z +$

$+4 \times threadIdx.y + threadIdx.x$

As a MB is composed of 16 blocks, the index of the MB is obtained by dividing the block index by 16.

## 4.2 Coefficients reading

Each thread reads the 16 coefficients of its block through one vectorized access using the built-in vector type longlong4 [25], whose definition is shown in Algorithm 4. Since the sizes of types long long int and short are 8 and 2 bytes, respectively, each member of the variable block\_vec contains 4 coefficients of the current block; as shown in Table 7, the member x contains the first 4 coefficients, the member y the next 4, and so on. Vectorized loads are an important CUDA optimization because they increase bandwidth and reduce both instruction count and latency [18].

In contrast, the solution of Su et al. uses the shared memory as a buffer to fulfill the requirement of coalesced global memory accesses recommended in CUDA literature [22, 25]. Since the maximum amount of shared memory per multiprocessor is 48 KB for GPUs with compute capability less than 3.7 [24] and the size of a block is 32 bytes, the occupancy is penalized in these architectures. For example, if the number of threads per thread-block is 128, the theoretical occupancy is reduced to 75% (3.x) or 67% (2.x) [24].

| <b>7</b> Mapping of block icients to longlong4 |        | Bits      |           |           |           |

|------------------------------------------------|--------|-----------|-----------|-----------|-----------|

| bers                                           | Member | 0–15      | 16–31     | 32–47     | 48–63     |

|                                                | x      | Coeff. 0  | Coeff. 1  | Coeff. 2  | Coeff. 3  |

|                                                | У      | Coeff. 4  | Coeff. 5  | Coeff. 6  | Coeff. 7  |

|                                                | z      | Coeff. 8  | Coeff. 9  | Coeff. 10 | Coeff. 11 |

|                                                | W      | Coeff. 12 | Coeff. 13 | Coeff. 14 | Coeff. 15 |

Table coeffic memb

```

Algorithm 4: CUDA built-in vector types

longlong4 and uchar2

struct __device_builtin_ __builtin_align_(16) longlong4

{

long long int x, y, z, w;

};

struct __device_builtin_ __align_(2) uchar2

{

unsigned char x, y;

};

```

## 4.3 Zigzag sorting

The coefficients of a block are extracted from the variable block\_vec and are written in the private array zz\_array in zigzag order. This operation is based on the mapping shown in Table 7. The performance of this operation is high for the following reasons. First, there are no dependencies between the different coefficient extractions; hence, the degree of instruction-level parallelism is high. Second, each coefficient extraction is performed with few operations of high throughput (two binary shifts and a cast). Third, zz\_array is placed in register space [22] because (1) it is small; (2) it is indexed with constant quantities, and (3) the kernel does not use more registers than available.

The solution of Su et al., after loading the blocks in shared memory, write them back to global memory in zigzag order; the coefficients will be read later again for calculating the CAVLC symbols. Conversely, CAVLCU executes the zigzag sorting in a much more efficient way, as it only consists of few high throughput operations with high degree of ILP reading and writing in the register space and saving costly memory global accesses.

## 4.4 Calculation of the symbols

Algorithm 5 shows the pseudocode for calculating the following symbols, which will be used for encoding the current block:

- The CAVLC symbols TotalCoeff, NumT1s and T1s.

- A 16-bit binary mask (*ZigzagArrayMask*) which represents the structure of the zigzag array and hence implicitly the CAVLC symbols TotalZeros and runs. If the i-th coefficient of the zigzag array is non-zero, the i-th most significant bit of the mask is 1; otherwise, this bit is 0. In the example of Fig. 1, the value of the mask is 1101101000000000.

- A second 16-bit binary mask (*ZigzagLevelsMask*) which represents the structure of the zigzag array excluding the trailing ones. In the example of Fig. 1, the value of the mask is 110000000000000.

## Algorithm 5: Calculation of symbols

```

#define MASK_OF_COEFF(coeff_idx) (1 << (15 - coeff_idx))</pre>

function calculate_symbols(// outputs

TotalCoeff, NumT1s, T1s,

ZigzagLevelsMask, ZigzagArrayMask,

// inputs

zz_array[16], MB_pred_mode

)

// Initialize symbols

NumT1s \leftarrow 0

T1s ← 0

ZigzagLevelsMask \leftarrow 0

ZigzagArrayMask \leftarrow 0

// Process AC coefficients

for coeff_idx = 15 to 1 step -1 do

if zz_array[coeff_idx] <> 0 then

update_symbols(// outputs

NumT1s, T1s,

ZigzagLevelsMask, ZigzagArrayMask,

// inputs

zz_array[coeff_idx],

MASK_OF_COEFF(coeff_idx)

)

end if

end for

if MB_pred_mode = INTRA_16 \times 16 then

ZigzagArrayMask \leftarrow (ZigzagArrayMask << 1)

else

// Process DC coefficient

if zz_array[0] <> 0 then

update_symbols(// outputs

NumT1s, T1s,

ZigzagLevelsMask, ZigzagArrayMask,

// inputs

zz_array[0],

MASK_OF_COEFF(0)

)

end if

end if

TotalCoeff ← __popc(ZigzagBlock_Mask)

end function

```

## Algorithm 6: Symbols updating from a non-zero coefficient

Each thread performs the next steps. First, it initializes all the symbols to 0. Second, for each nonzero AC coefficient stored in zz\_array (i.e., all but the first), from the last to the first, it updates all the symbols except TotalCoeff performing the steps presented in Algorithm 6. Third, if the prediction mode of the current MB is not Intra 16×16, it processes the DC coefficient (i.e., the first) in the same way as in step 2. Otherwise, it ignores the DC coefficient and left-shift the symbol ZigzagArrayMask one bit, as only the subblock formed by the AC coefficients must be considered. Fourth, it calculates TotalCoeff from ZigzagArrayMask using the CUDA function \_\_popc [23], which counts the number of bits that are set to 1 in a 32 bit integer. The throughput of \_\_popc is high as it compiles to a single instruction [25].

In the solution of Su et al., each thread iterates two times over the coefficients of a block for calculating its CAVLC symbols: TotalCoeff in the first iteration and the remaining ones (NumT1s, T1s, levels, TotalZeros, runs) in the second. All the symbols are written in global memory and later read for transferring them between the corresponding kernels. CAVLCU optimizes significantly this process for the following reasons. First, it iterates only one time over the coefficients of a block for calculating the necessary symbols. Second, the number of symbols processed in the loop is reduced to only 4 integers: NumT1s, T1s, *ZigzagLevelsMask* and ZigzagArrayMask. Third, as shown in Algorithm 6, the update of the symbols in each loop iteration is performed very efficiently, as it only requires two OR operations for the symbols ZigzagLevelsMask and ZigzagArrayMask, an addition for NumT1s and a binary left shift, an OR operation and a comparison for T1s. Fourth, our algorithm saves read/write global memory operations performed by the solution of Su et al. as transferring symbols between kernels is not required.

Fig. 11 Transmission of parameter nA through global memory

## 4.5 Calculation of parameter nC

According to the method described in Subsection 2.1.1, each thread calculates the parameter nC of its block from the information associated to the left and top neighbouring blocks (*info\_A* and *info\_B*, respectively). Each block information is composed of the symbol TotalCoeff and the slice ID. The symbols TotalCoeff of the left and top blocks are the parameters nA and nB, respectively. The slice ID of the left and top blocks will be denoted as *SliceID\_A* and *SliceID\_B*, respectively.

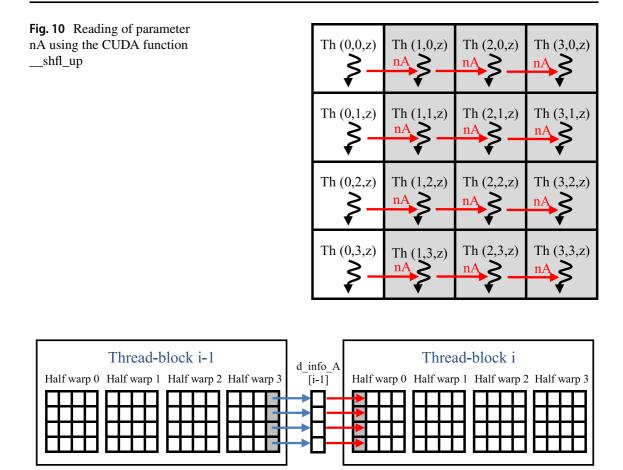

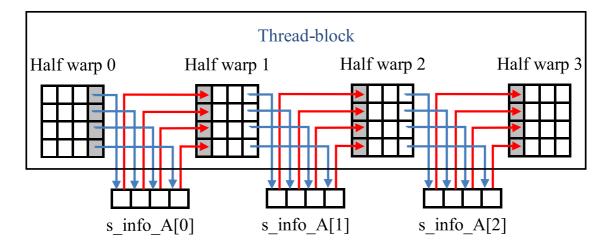

Each thread (x, y, z) gets info\_A as follows. If the current block is not in the first column of its MB, nA is read from the left thread (x - 1, y, z) using the CUDA function  $\_shfl\_up$  [25], as shown in Fig. 10. As both left and current block are in the same MB, SliceID\_A is the slice ID of the current MB. If the current block is in the first column of the first MB of a region, info\_A is read from an intermediate array in global memory ( $d\_info\_A$ ) of dimensions NUM\_REG×4. As illustrated in Fig. 11, each thread (0, y, 0) of a thread-block i reads info\_A from the element d\_ info\_A[i - 1][y], which is written by the thread (3, y, REG\_SIZE - 1) of the thread-block i - 1. If the current block is in the first column of the second or posterior MB of a region, info\_A is read from an intermediate array in shared memory ( $s\_info\_A$ ) of dimensions REG\_SIZE×4. As illustrated in Fig. 12, each thread (0, y, z) with z > 0 of a thread-block reads info\_A from the element s\_info\_A[z - 1][y], which is written by the thread in Fig. 12, each thread (0, y, z) with z > 0 of a thread-block reads info\_A from the element s\_info\_A[z - 1][y], which is written by the thread in Fig. 12, each thread (0, y, z) with z > 0 of a thread-block reads info\_A from the element s\_info\_A[z - 1][y], which is written by the thread (3, y, z - 1].

Fig. 12 Transmission of parameter nA through shared memory

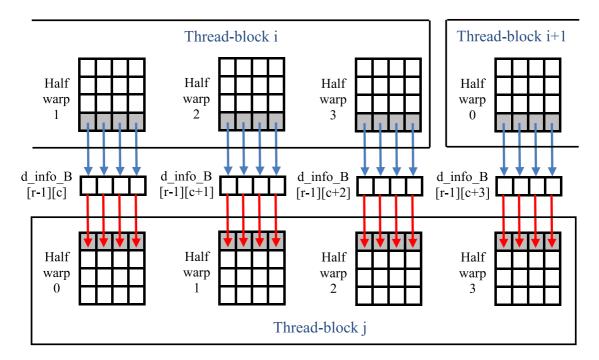

In a similar way, each thread (x, y, z) gets info\_B as follows. If the current block is not in the first row of its MB, nB is read from the top thread (x, y - 1, z) using the CUDA function  $\_shfl\_up$  [25], as shown in Fig. 13. As both top and current block are in the same MB, SliceID\_B is the slice ID of the current MB. If the current block is in the first row of its MB, info\_B is read from an intermediate array in global memory ( $d\_info\_B$ ) of dimensions NUM\_MB\_VER×NUM\_MB\_ HOR×4, where  $NUM\_MB\_VER$  and  $NUM\_MB\_HOR$  are the number of MBs in the vertical and horizontal dimensions of the frame, respectively. As illustrated in Fig. 14, each thread (x, 0, z) of a thread-block reads info\_B from the element d\_info\_B[r-1][c][x], where r and c are, respectively, the row and the column of the current MB. Each element d\_info\_B[r][c][x] is written by the thread (x, 3, z) of the halfwarp that processes the MB in row r and column c.

Algorithm 7 shows the pseudocode for managing the parameter nC. Each thread performs the next steps. First, it represents the necessary information of the current block (the symbol TotalCoeff and the slice ID of its MB) in a compact way using a 32-bit integer (*info*), where the 5 least significant bits store TotalCoeff, the sixth

| Th (0,0,z)       | Th (1,0,z)       | $\mathbf{N}$ | Th (2,0,z)    | Th (3,0,z)    |

|------------------|------------------|--------------|---------------|---------------|

| nB<br>Th (0,1,z) | nB<br>Th (1,1,z) | -            | nB Th (2,1,z) | nB Th (3,1,z) |

| nB               | nB               | M.           | nB            | nB            |

| Th (0,2,z)       | Th (1,2,z)       |              | Th (2,2,z)    | Th (3,2,z)    |

| nB               | nB               | N.           | nB            | nB            |

| Th (0,3,z)       | Th (1,3,z)       |              | Th (2,3,z)    | Th (3,3,z)    |

Fig. 13 Reading of parameter nB using the CUDA function \_\_shfl\_up

Fig. 14 Transmission of parameter nB through global memory

least significant bit is set to 1, which ensures info is nonzero, and the 16 most significant bits store the slice ID. Second, it calculates the indexes of the row and the column of the MB in the frame. Third, if proceeds, writes info in the intermediate arrays as described above. Fourth, it synchronizes with other threads of the block for ensuring the array s\_info\_A contains the correct values. Fifth, it gets nA and nB as explained above. If a neighbouring block is unavailable, the corresponding reading function (*read\_nA* or *read\_nB*) returns -1. Sixth, it calculates nC from nA and nB using the method shown in Table 2.

Algorithm 7: Management of parameter nC

```

function manage_nC(TotalCoeff, MB_slice, blk_idx, MB_idx)

info ← (MB_slice << 16) + 64 + TotalCoeff

write_info_B_of_right_MB(info, MB row, MB col)

write_info_A_of_right_MB(info, MB col)

_syncthreads()

if nA = -1 and nB = -1 then

nC ← 0

else if nB = -1 then

nC \leftarrow nA

else if nA = -1 then

nC ← nB

else

nC \leftarrow (nA + nB + 1) >> 1

end if

return nC

end function

```

As in our previous works [7, 8], the thread-block synchronization mechanism proposed by Yan et al. [47] is used for synchronizing the reads with the writes in global memory. In this case, it is applied on both horizontal (d\_info\_A) and vertical (d\_info\_B) dimensions and the reads are performed using atomic operations. The elements of d\_info\_A and d\_info\_B are initialized to 0 statically. Since all the values written are nonzero (due to the fact that the sixth least significant bit is set to 1), the read of each element is performed executing the CUDA atomic function *atomicExch* [25] repeatedly until a nonzero value is returned. Additionally, the use of this function restores the stored value to 0, which allows subsequent uses of the intermediate arrays in global memory, and avoids getting old cached values.

As static initialization of variables in shared memory is illegal in CUDA, a different synchronization mechanism is used in the accesses to s\_info\_A. In this case, the CUDA intrinsic function *\_\_syncthreads()* guarantees that each element is not read until its value has been written. On the other hand, the use of the keyword *volatile* in the declaration of the array s\_info\_A ensures any reference to this variable compiles to an actual memory read or write instruction [25].

CAVLCU reduces significantly the number of global memory accesses with respect to the solution of Su et al. for the following reasons. First, in our solution, each thread-block, on the one hand, only writes in global memory the symbols TotalCoeff of the last column and the last row of its region and, consequently, on the other hand, only reads from global memory the parameters nA and nB of the first column and the first row, respectively. In contrast, the solution of Su et al. writes all the symbols TotalCoeff of the frame in global memory and each thread-block not only reads from global memory the parameters nA and nB of the first column and the first row of the frame in global memory and each thread-block not only reads from global memory the parameters nA and nB of the first column and

the first row of its region but also all the symbols TotalCoeff of the region. Second, in the approach of Su et al., once the parameters nC are calculated, they are written in global memory to be read in the coding stage. Therefore, CAVLCU saves two operations in global memory for writing and reading all the parameters nC of a frame.

## 4.6 Block encoding

The first action of this stage is to call the CUDA warp synchronization function \_\_\_\_\_\_ *syncwarp()* [25] to force reconvergence. This prevents the independent thread scheduling of modern architectures (Volta and later) from increasing the number of global memory writes.

Each thread i of the grid writes the encoding of its block in the subvector i of BLK\_ENC\_SIZE elements ( $d\_blk\_enc$ ) of d\_enc\_words (see Fig. 7), and the bitlength of the encoding in the element i of d\_enc\_lens.

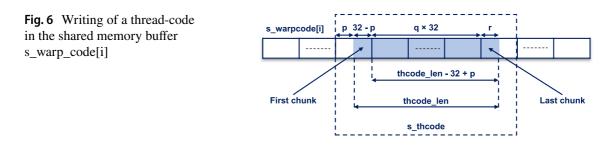

The block encoding is constructed in the way specified in Sect. 2. As the VLCs assigned to the CAVLC symbols are obtained, their bits are concatenated in a 32-bit variable (*word\_val*) and their lengths added in a second 32-bit variable (*word\_len*) while the bit-length of the resulting encoding is less than or equal to 32. When the last condition is not satisfied, the first 32 bits of the resulting encoding are written in the corresponding element of d\_blk\_enc, and the value and length of the remaining encoding are stored in word\_val and word\_len, respectively. The process continues until all the VLCs are written. The bit-length of the encoding is written in the element i of d\_enc\_lens. Its value is calculated using the following expression, where word\_idx is the index of the last accessed position of d\_blk\_enc:

word\_idx  $\times$  32 + word\_len

The lookup tables of the symbols CoeffToken, TotalZeros and runs are stored in arrays in global memory, which are initialized statically. The base type is the CUDA intrinsic vector type *uchar2* [25], whose definition is presented in Algorithm 4. The members x and y represent, respectively, the bit-length and the value of a variable-length code. The CUDA function \_\_ldg [25] is used for caching the reads in the read-only data cache [22]. In contrast, the solution of Su et al. uses the shared memory for caching the lookup tables. Both memory systems have a small latency but the use of the read-only data cache saves a synchronization barrier and additional instructions for caching the lookup tables programmatically.

The VLCs of the levels are calculated using the method for encoding levels without lookup tables presented by Hoffman et al. [11]. The values of the levels are extracted from the variable block\_vec using the positions stored in the symbol ZigzagLevelsMask.

The symbols TotalZeros and runs are obtained from the positions in reverse order of the nonzero coefficients in the zigzag array. As illustrated in Table 8 for the example of Fig. 1, the coefficients positions are 0 for the last coefficient, 1 for the penultimate coefficient, and so on. In the case of TotalZeros the following expression is used:

| Table o Coefficients po | osition | S 01 ZI | gzag a | array c | n rig. | 1  |   |   |   |   |   |   |   |   |   |   |